## T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | A Study of 300GHz-Band CMOS Phased-Array Transceiver System for High Data Rate Wireless Communication                                                                                        |

| 著者(和文)            | ABDOIbrahim Imad Ibrahim                                                                                                                                                                     |

| Author(English)   | Ibrahim Imad Abdo                                                                                                                                                                            |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12155号,<br>报与年月日:2021年12月31日,<br>学位の種別:課程博士,<br>審査員:岡田 健一,髙木 茂孝,德田 崇,廣川 二郎,伊藤 浩之,SONG Ho-Jin                                                          |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12155号,<br>Conferred date:2021/12/31,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                         |

| Type(English)     | Doctoral Thesis                                                                                                                                                                              |

## A Study of 300GHz-Band CMOS Phased-Array Transceiver System for High Data Rate Wireless Communication

by

Ibrahim Imad Ibrahim Abdo

A Ph. D. dissertation submitted in partial satisfaction of the requirements for the degree of

## **Electrical and Electronic Engineering**

in the

## **School of Engineering**

of

## **Tokyo Institute of Technology**

Supervised by

Prof. Kenichi Okada

Winter 2021

To my family,

## Acknowledgment

I would first like to thank my academic advisor, Professor Kenichi Okada for giving me the chance to be a part of his Laboratory and Tokyo Institute of Technology. I am very grateful to Professor Kenichi Okada for guiding my research. Despite his very busy schedule, he was always there to help me whenever I ran into a trouble spot or had a question about my research. His passion and ambition to achieve what nobody else could achieve drives me to reach my highest potential. He is an actual world-class professor, and I am proud to be his student.

I am also thankful to Professor Atsushi Shirane for the continuous support and the helpful discussions. He was always accessible and willing to help with my research.

I would like to thank the thesis examination committee members, Professor Shigetaka Takagi, Professor Takashi Tokuda, Professor Jiro Hirokawa, Professor Hiroyuki Ito, and Professor Ho-Jin Song for spending their precious time and for their invaluable comments and suggestions to improve the quality of my thesis.

In addition, I would like to thank Ms. Yoshino Kasuga for her great help in the lab life and the everyday life issues despite her busy schedule. I am very grateful to her for her kindness.

I also would like to express my gratitude to the research group members Dr. Korkut Kaan Tokgoz, Takuya Fujimura, Tsuyoshi Miura, Chun Wang, Carrel da Gomez, Qi Li, Kota Hatano, Hans Herdian, Chenxin Liu, Abanob Shehata, and Wenbin Zheng for supporting me during my studies.

I am also grateful to Mr. Hiroshi Hamada and Professor Hideyuki Nosaka for their continuous help and support during my internship in NTT laboratories and throughout the joint research period.

I would also like to thank all the students of Okada Laboratory for their help and support, especially Dr. Jian Pang, Mr. Kiyoshi Yanagisawa, Waleed Madany, Ashbir Aviat Fadila, Atsuhiro Kawaguchi, and Michihiro Ide who helped me numerous times.

I would like to express my sincere gratitude to the Japanese government for providing me its precious support. I will always be thankful to Japan for giving me such a great experience. Finally, I would like to thank my parents and my two sisters. Their endless love, support and self-sacrifices have made me the person I am today.

## **Abstract**

This dissertation presents a study of 300GHz-band CMOS transceiver and phased-array systems that are based on subharmonic mixing. 300GHz-band is one of the main candidates for the next generation of wireless communication systems (6G). This thesis covers the design details of the transceiver RF front-end including the mixers, LO chain components, and the PCB implementation for the phased-array system. Using the CMOS process to build 300GHz-band transceivers is an attractive option considering the low cost and the compatibility with the digital integrated circuits. However, the main obstacle resides in the low maximum oscillation frequency ( $f_{\text{max}}$ ) of the CMOS transistors which barely exceeds 300GHz for small transistor sizes. As a result, the implementation of reliable power amplifiers (PAs) and low noise amplifiers (LNAs) is quite difficult and still not demonstrated well in the literature. Most of the recent works eliminate the RF amplifiers and adopt the mixer-last transmitter (TX), mixer-first receiver (RX) architecture instead. The design using the mentioned architecture is still challenging considering that the linearity and noise requirements of the mixers are very critical. In addition, the free space path loss of the 300GHz-band is approximately 20dB higher than the loss of the currently popular 5G bands around 30GHz, making it more difficult to achieve the required signal-to-noise-ratio (SNR) for a long-distance high-data-rate wireless link. Overcoming the SNR degradation may cause a drastic increase in the area and the power consumption, so careful design and implementation techniques are necessary. Two 300GHz-band transceiver systems are discussed in this thesis; a low-power transceiver with a singlemixing-path, and a phased-array transceiver with output power improvement and image rejection techniques. The low-power transceiver utilizes a subharmonic mixer with novel circuit techniques to provide suitable system performance and to meet the link budget requirements. The subharmonic mixer is chosen in this work to reduce the LO frequency and the design complexity. Other parts such as the LO chain components are also designed using special circuit techniques to reduce the overall power consumption. The transceiver proposed in this thesis achieves a 34Gb/s maximum data rate over a 1cm distance while consuming 0.41W from a 1V supply. Compound semiconductor (InP) PAs and LNAs are added to the system to study the "hybrid-transceiver" option, and as a result, the maxvi Abstract

imum data rate is improved to 56Gb/s with higher order modulations such as 64QAM becoming usable as well. The phased-array transceiver utilizes the subharmonic mixer with a bi-directional architecture. The TX mode is based on the outphasing technique to improve the average output power, and the RX mode adopts the Hartley architecture to cancel any undesired image signals. Thanks to the bi-directional operation, the TX and the RX share the antenna, and that makes it easier to implement a phased-array due to the small chip size. The measured beam range of the implemented array is from -18° to 18°. The maximum data rate of the TX mode is 52Gb/s and the maximum data rate of the RX mode is 36Gb/s. Apart from the systems mentioned above, the thesis also explores frequency multiplication techniques at mm-wave frequencies due to their critical role in sub-THz systems in general. The introduced systems are implemented in 65nm CMOS technology and the effectiveness of the proposed techniques was verified in clean-room and over-the-air measurements.

## **Contents**

| A  | cknov  | vledgment                                    | ii |

|----|--------|----------------------------------------------|----|

| Al | ostrac | et e                                         | •  |

| 1  | Intr   | oduction                                     | 1  |

|    | 1.1    | Standards and Regulations for 300GHz-band    | 3  |

|    | 1.2    | 300GHz-band CMOS Transceivers                | 4  |

|    | 1.3    | Overview of This Thesis                      | 5  |

| 2  | 3000   | GHz-Band CMOS Phased-Array Design Challenges | 7  |

|    | 2.1    | $f_{\max}$ of the CMOS Transistor            | 7  |

|    | 2.2    | LO Generation                                | 10 |

|    | 2.3    | Error Vector Magnitude                       | 11 |

|    | 2.4    | FSPL and Beamforming                         | 12 |

|    | 2.5    | Challenges for 300GHz-band Phased-Array      | 13 |

|    |        | 2.5.1 Antenna Implementation and Connection  | 13 |

|    |        | 2.5.2 Antenna Placement and Spacing          | 14 |

|    |        | 2.5.3 Power Consumption                      | 15 |

|    |        | 2.5.4 Manufacturing Cost                     | 15 |

| 3  | Free   | quency Multipliers for LO Generation         | 17 |

|    | 3.1    | Frequency Multiplier Topologies              | 17 |

|    | 3.2    | Millimeter-Wave Frequency Triplers           | 19 |

|    |        | 3.2.1 Proposed Single-Ended Tripler          | 20 |

|    |        | 3.2.2 Proposed Differential Tripler          | 29 |

|    | 3.3    | Push-Push Doubler                            | 32 |

| 4  | Sub    | harmonic-Mixer-Based 300GHz-Band Transceiver | 39 |

|    | 4.1    | Proposed Transceiver Architecture            | 40 |

|    | 42     | Circuit Implementation                       | 40 |

viii CONTENTS

|   |      | 4.2.1    | Push-Push Subharmonic Mixer                             | . 41  |

|---|------|----------|---------------------------------------------------------|-------|

|   |      | 4.2.2    | LO Chain                                                | . 46  |

|   |      | 4.2.3    | IF Amplifiers                                           | . 48  |

|   | 4.3  | Measu    | rement Results of the CMOS Transceiver                  | . 50  |

|   | 4.4  | InP-CN   | MOS Hybrid Transceiver                                  | . 57  |

|   | 4.5  | Measu    | rement Results of the Hybrid Transceiver                | . 60  |

|   | 4.6  | Conclu   | asion                                                   | . 63  |

| 5 | Bi-D | irection | nal 300GHz-Band Phased-Array Transceiver                | 65    |

|   | 5.1  | Phased   | l-Array Transceiver Architecture                        | . 67  |

|   |      | 5.1.1    | Outphasing Transmitter with LOFT Cancellation           | . 67  |

|   |      | 5.1.2    | Hartley Receiver                                        | . 71  |

|   | 5.2  | Circuit  | t Implementation                                        | . 72  |

|   |      | 5.2.1    | LO Chain                                                | . 72  |

|   |      | 5.2.2    | IF Distributed Amplifiers                               | . 77  |

|   | 5.3  | PCB a    | nd Phased-Array Implementation                          | . 79  |

|   | 5.4  | Measu    | rement Results                                          | . 83  |

|   | 5.5  | Conclu   | asion                                                   | . 91  |

| 6 | Con  | clusion  | and Future Work                                         | 93    |

|   | 6.1  | Conclu   | asion                                                   | . 93  |

|   | 6.2  | Future   | Directions                                              | . 94  |

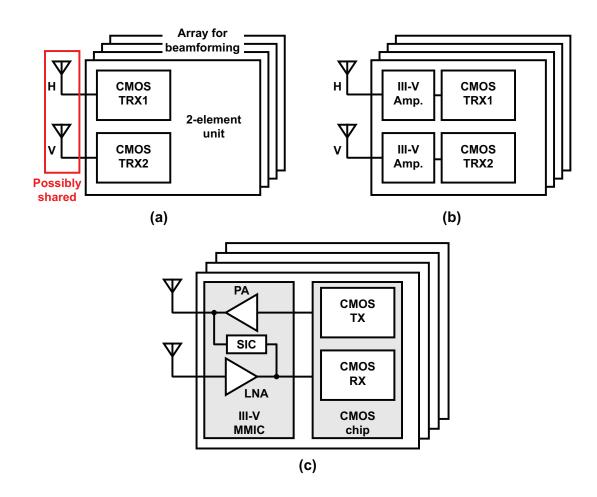

|   |      | 6.2.1    | Boosting the Output Power                               | . 96  |

|   |      | 6.2.2    | Two Dimensional Phased-Array                            | . 97  |

|   |      | 6.2.3    | Options for Enhanced Implementation                     | . 98  |

|   |      | 6.2.4    | Hybrid Transceiver Board/Module                         | . 100 |

|   |      | 6.2.5    | Maximizing the Data Rate to Leverage the Wide Bandwidth | . 100 |

| A | Pub  | lication | List                                                    | 113   |

|   | A.1  | Journa   | l Papers                                                | . 113 |

|   | A.2  | Interna  | ational Conferences and Workshops                       | . 113 |

|   | A.3  | Domes    | stic Conferences and Workshops                          | . 114 |

|   | A.4  | Co-Au    | thor                                                    | . 115 |

|   |      | A.4.1    | Journals and Letters                                    | . 115 |

|   |      | A 4 2    | Conferences                                             | . 115 |

## **List of Figures**

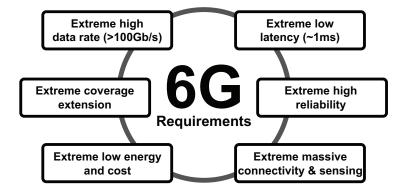

| 1.1 | 6G technology requirements                                                   | 2  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | 6G technology possible applications                                          | 2  |

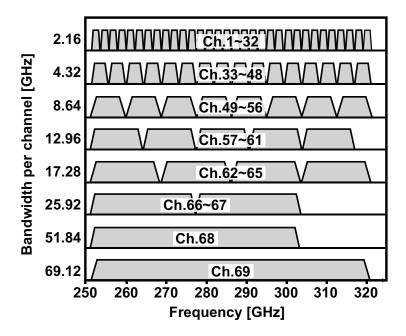

| 1.3 | IEEE Std. 802.15.3 channel plan                                              | 4  |

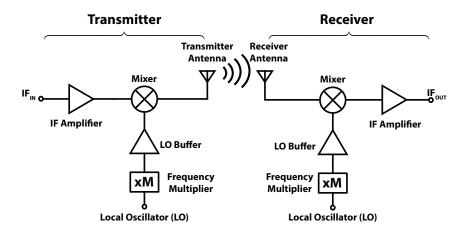

| 1.4 | Generic architecture for the 300GHz-band transceiver                         | 5  |

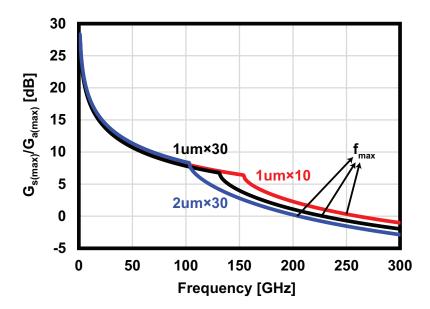

| 2.1 | Simulated maximum available/stable gain for several transistor sizes in      |    |

|     | 65nm CMOS process                                                            | 8  |

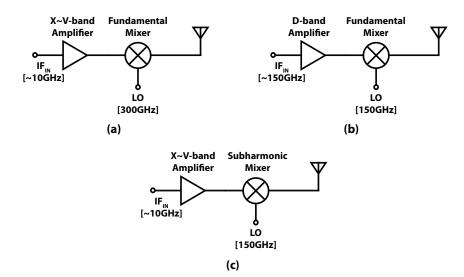

| 2.2 | Possible 300GHz-band system architecture options for different LO fre-       |    |

|     | quencies. (a) Simple fundamental mixing. (b) Both LO and IF are in the       |    |

|     | D-band. (c) Subharmonic mixing.                                              | 9  |

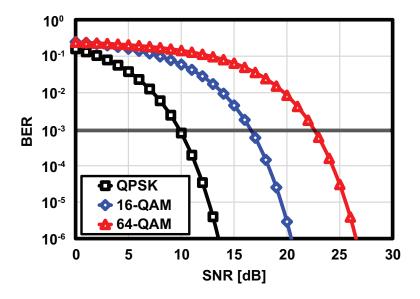

| 2.3 | Calculated BER against SNR for several modulation schemes                    | 12 |

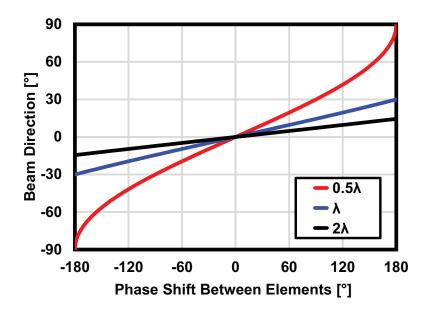

| 2.4 | Beam steering range for different antenna pitch lengths                      | 15 |

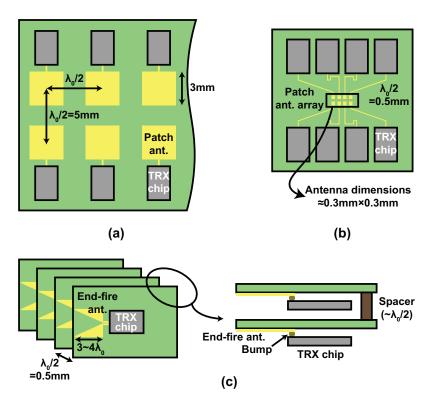

| 2.5 | Phased-array implementation issue at 300GHz-band. (a) 28GHz phased-          |    |

|     | array structure. (b) Using the same structure for 300GHz. (c) Proposed       |    |

|     | stacked architecture                                                         | 16 |

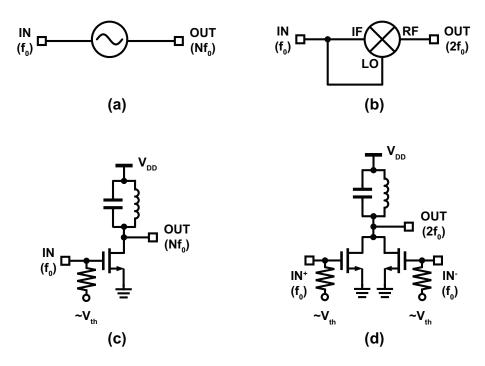

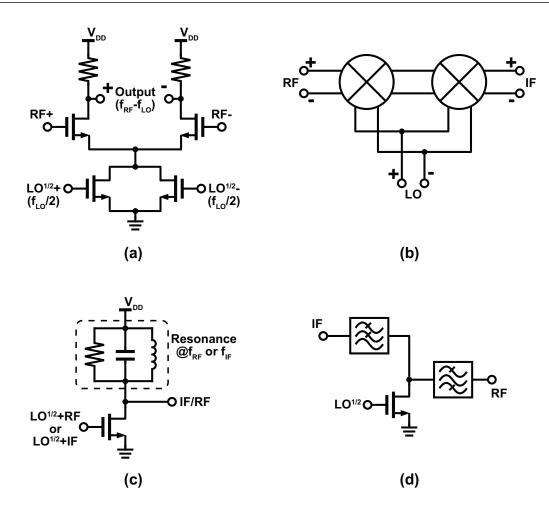

| 3.1 | Conventional frequency multiplier topologies: (a) Injection-lock-based,      |    |

|     | (b) Mixer-based, (c) Device nonlinearity-based, and (d) Push-push-based.     | 18 |

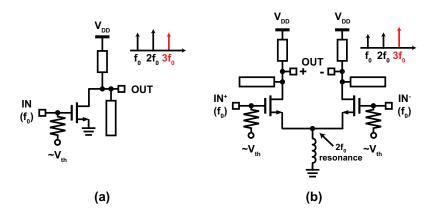

| 3.2 | Conventional device nonlinearity-based frequency triplers: (a) Single-       |    |

|     | ended, (b) Differential with second harmonic resonance at the tail node      | 19 |

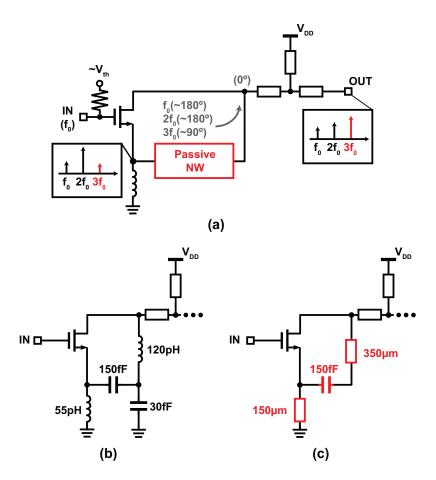

| 3.3 | Proposed fundamental and second harmonic rejection technique. (a) The        |    |

|     | feedback network operation. (b) The circuit built using lumped compo-        |    |

|     | nents. (c) The proposed circuit                                              | 20 |

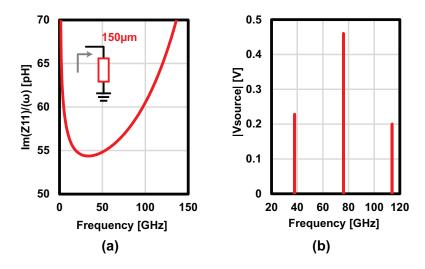

| 3.4 | (a) The inductance of the tail transmission line. (b) The voltage magnitude  |    |

|     | at the source for all the harmonics. (f0=38GHz, PIN=10dBm)                   | 21 |

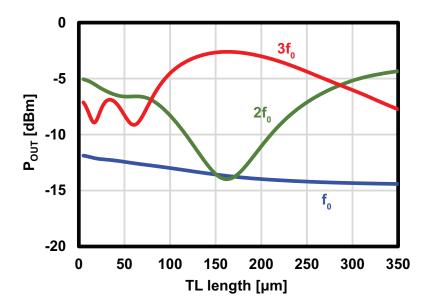

| 3.5 | Simulated output power of the frequency tripler for different tail transmis- |    |

|     | sion line lengths. ( $f_0$ =38GHz, $P_{IN}$ =10dBm)                          | 22 |

| 3.6 | Simulated output power of the frequency tripler for different feedback       |    |

|     | transmission line lengths. ( $f_0$ =38GHz, $P_{IN}$ =10dBm)                  | 22 |

| 3.7  | Frequency tripler simulated operation: (a) The simulated currents, (b) The simulated phase difference between the drain and the feedback currents. $(f_0=38\text{GHz}, P_{\text{IN}}=10\text{dBm})$ | 23 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8  | Frequency tripler simulated operation: (a) Current waveforms of fundamental signals, (b) second harmonic signals, and (c) third harmonic signals ( $f_0$ =38GHz, $P_{IN}$ =10dBm)                   | 24 |

| 3.9  | Proposed frequency tripler circuit schematic                                                                                                                                                        | 25 |

| 3.10 | Frequency tripler micrograph. (© 2021 IEICE)                                                                                                                                                        | 25 |

| 3.11 | Measurement setup                                                                                                                                                                                   | 26 |

| 3.12 | Tripler measured and simulated output power. (input power = $10dBm$ )                                                                                                                               | 26 |

| 3.13 | Tripler measured and simulated fundamental rejection ratio. (input power                                                                                                                            |    |

|      | = 10dBm)                                                                                                                                                                                            | 28 |

| 3.14 | Tripler measured and simulated output power and Conversion gain                                                                                                                                     | 28 |

| 3.15 | Fundamental rejection stub (a) schematic (b) simulated stub impedance, (c) smith chart                                                                                                              | 29 |

| 3.16 | Tripler circuit (input signal frequency = $f_0$ = 38–39GHz): (a) Conventional differential tripler. (b) Proposed tripler circuit                                                                    | 30 |

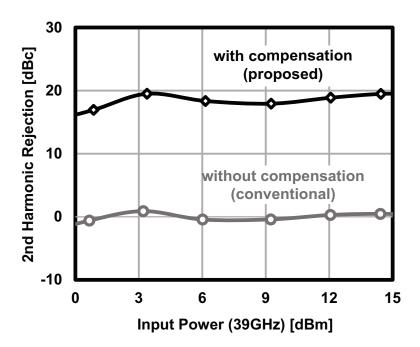

| 3.17 | Proposed tripler simulated output power and the comparison with the conventional architecture                                                                                                       | 31 |

| 3.18 | Proposed tripler simulated 2nd harmonic rejection and the comparison                                                                                                                                |    |

|      | with the conventional architecture                                                                                                                                                                  | 32 |

| 3.19 | Conventional push-push frequency doubler and its operation                                                                                                                                          | 33 |

| 3.20 | Proposed modified push-push frequency doubler                                                                                                                                                       | 33 |

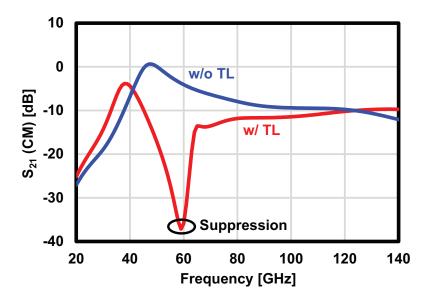

| 3.21 | The effect of the balun mismatch compensation line on the common mode                                                                                                                               |    |

|      | signal                                                                                                                                                                                              | 34 |

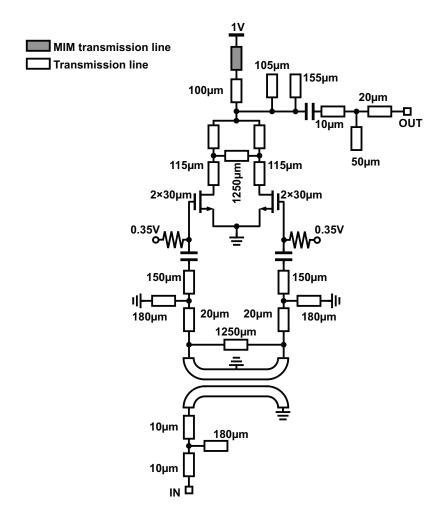

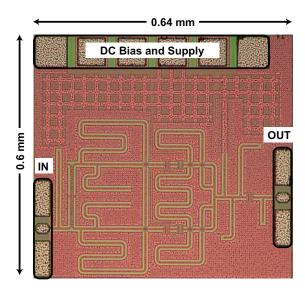

| 3.22 | Proposed push-push frequency doubler detailed schematic                                                                                                                                             | 35 |

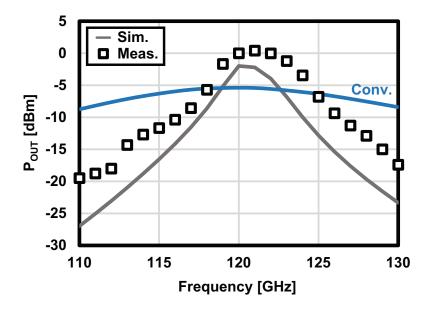

| 3.23 | Proposed push-push frequency doubler micrograph. (© 2021 IEICE)                                                                                                                                     | 36 |

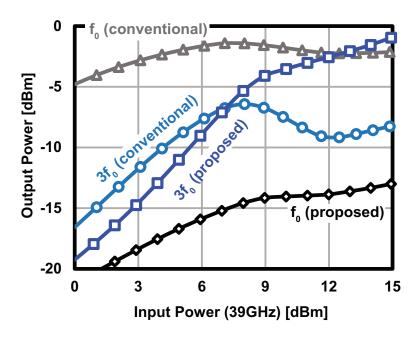

| 3.24 | Push-push frequency doubler measured and simulated output power                                                                                                                                     | 36 |

| 3.25 | Push-push frequency doubler measured and simulated fundamental rejec-                                                                                                                               |    |

|      | tion ratio                                                                                                                                                                                          | 37 |

| 3.26 | Push-push frequency doubler measured and simulated output power and Conversion gain                                                                                                                 | 37 |

| 4.1  | Proposed transceiver block diagram                                                                                                                                                                  | 40 |

| 4.2  | Target frequency band and the covered IEEE Std. 802.15.3d channels                                                                                                                                  | 41 |

LIST OF FIGURES xi

| 4.3  | Conventional CMOS subharmonic mixer circuits. (a) Push-push LO dou-       |    |

|------|---------------------------------------------------------------------------|----|

|      | bling, (b) 2-stage mixing, (c) transconductance mixer, and (d) resistive  |    |

|      | mixer                                                                     | 42 |

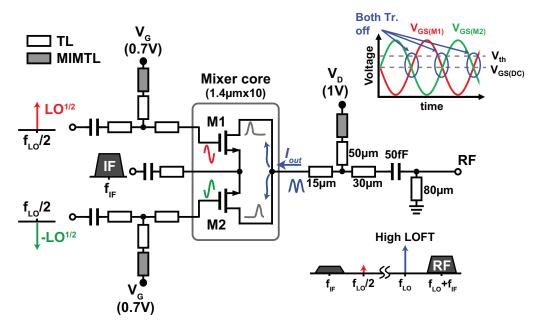

| 4.4  | Schematic and operation of the push-push subharmonic mixer                | 43 |

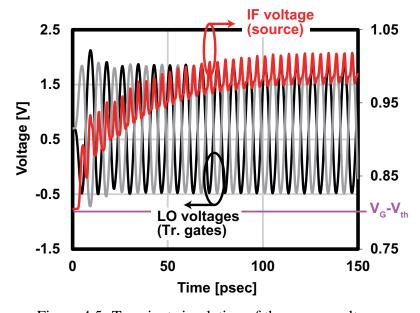

| 4.5  | Transient simulation of the source voltage                                | 43 |

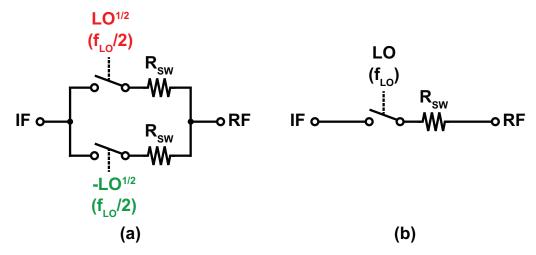

| 4.6  | (a) Switching operation of the proposed mixer and (b) the equivalent cir- |    |

|      | cuit with second harmonic switching.                                      | 44 |

| 4.7  | Proposed mixer biasing technique                                          | 45 |

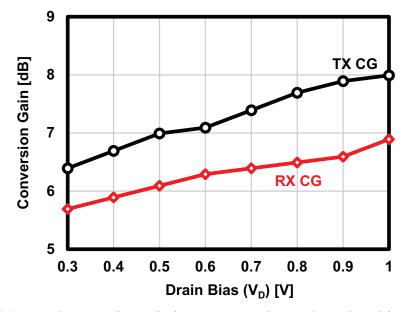

| 4.8  | Measured conversion gain improvement due to the reduced junction ca-      |    |

|      | pacitance                                                                 | 45 |

| 4.9  | LO chain circuit schematic                                                | 46 |

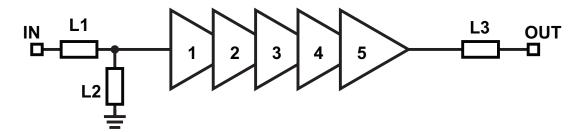

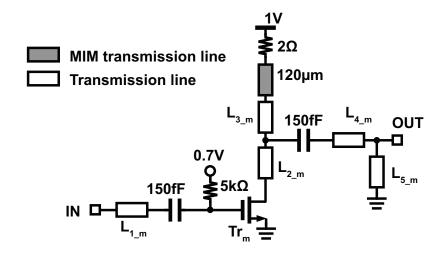

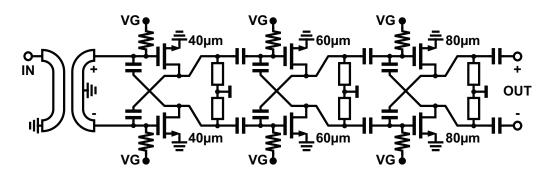

| 4.10 | 5-stage IF amplifier                                                      | 47 |

| 4.11 | V-band IF amplifier single-stage schematic                                | 47 |

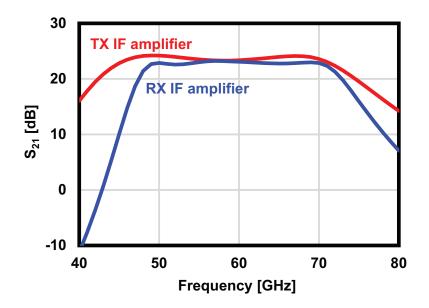

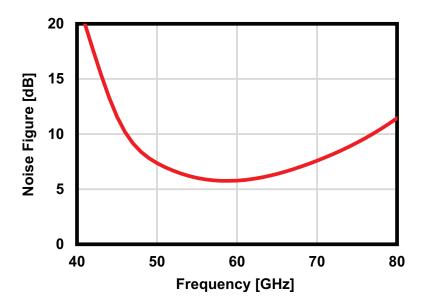

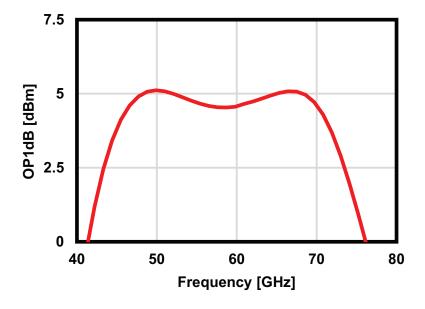

| 4.12 | Simulated IF amplifiers gain characteristics                              | 48 |

| 4.13 | Simulated RX IF amplifier noise figure                                    | 49 |

| 4.14 | Simulated TX IF amplifier OP1dB                                           | 49 |

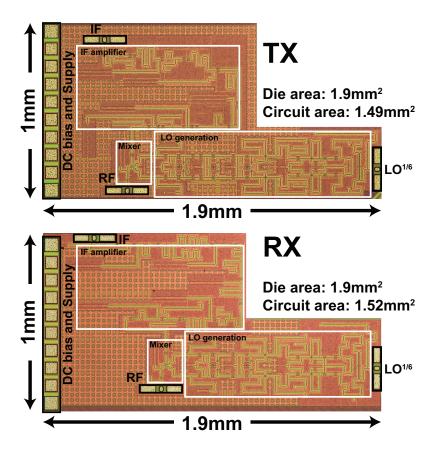

| 4.15 | CMOS TX and RX chip photos. (© 2020 IEEE)                                 | 50 |

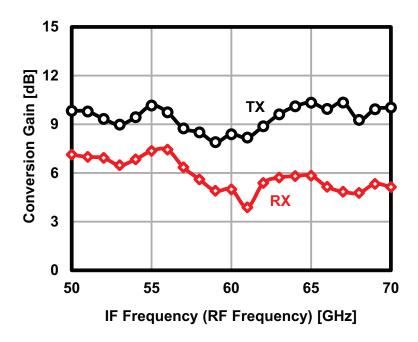

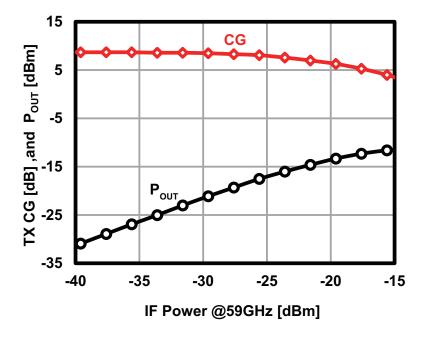

| 4.16 | Measured TX and RX conversion gain values                                 | 51 |

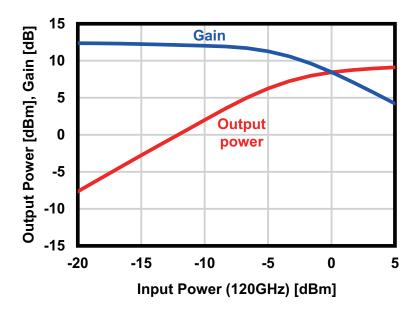

| 4.17 | Measured TX input/output power characteristics                            | 51 |

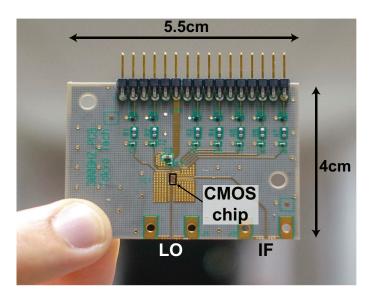

| 4.18 | PCB for OTA evaluation. (© 2020 IEEE)                                     | 52 |

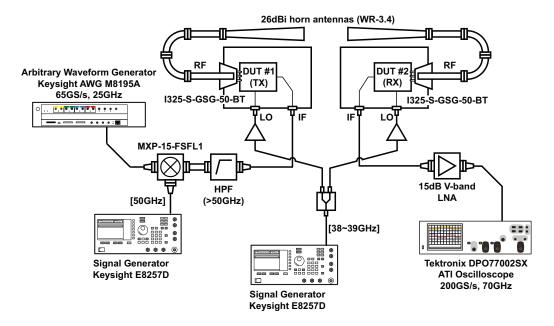

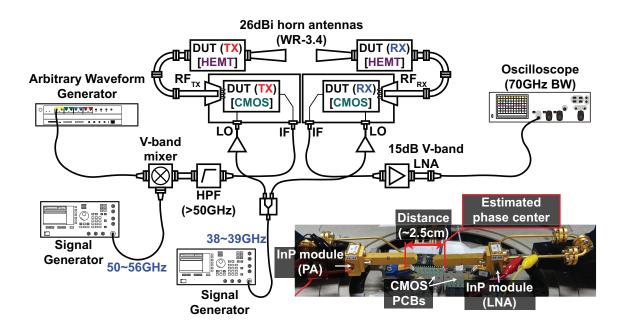

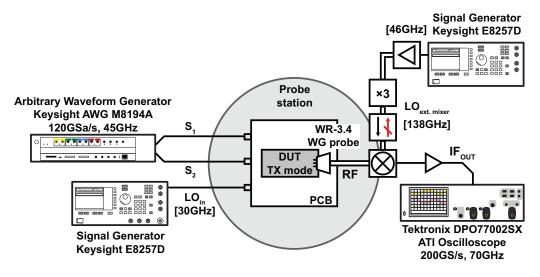

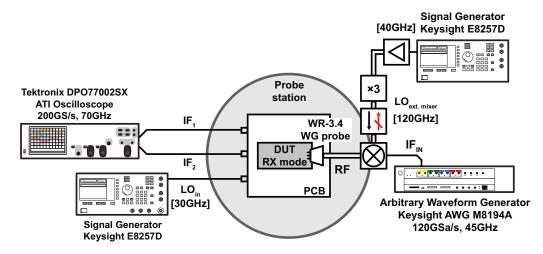

| 4.19 | CMOS transceiver measurement setup                                        | 52 |

| 4.20 | CMOS transceiver measurement setup photo. (© 2020 IEEE)                   | 53 |

| 4.21 | Performance summary for maximum data rate conditions                      | 53 |

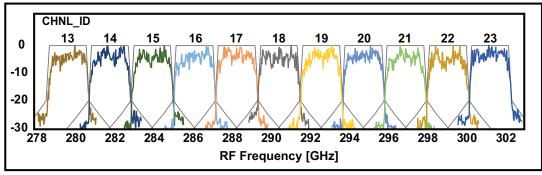

| 4.22 | Performance summary for IEEE Std. 802.15.3d channels                      | 54 |

| 4.23 | Measured spectrum of IEEE Std. 802.15.3d channels having CHNL_ ID         |    |

|      | 13 to 23                                                                  | 54 |

| 4.24 |                                                                           | 55 |

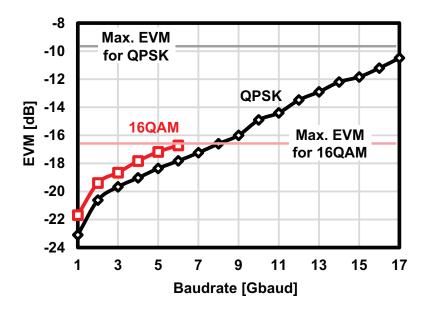

| 4.25 | Measured EVM versus baud rate for 4cm distance                            | 55 |

| 4.26 | Block diagram of the hybrid transceiver with the simplified schematic of  |    |

|      | the CMOS part                                                             | 57 |

| 4.27 | Detailed performance parameters used to calculate the SNDR of the hy-     |    |

|      | brid transceiver.                                                         | 58 |

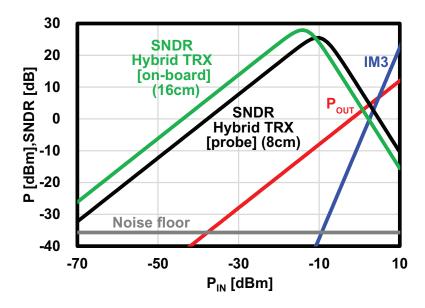

| 4.28 |                                                                           | 59 |

|      | • • • • • • • • • • • • • • • • • • • •                                   | 59 |

|      |                                                                           | 60 |

|      | •                                                                         | 61 |

|      | •                                                                         | 61 |

| 4.33 | Hybrid transceiver performance summary. (© 2021 IEICE)                       | 62 |

|------|------------------------------------------------------------------------------|----|

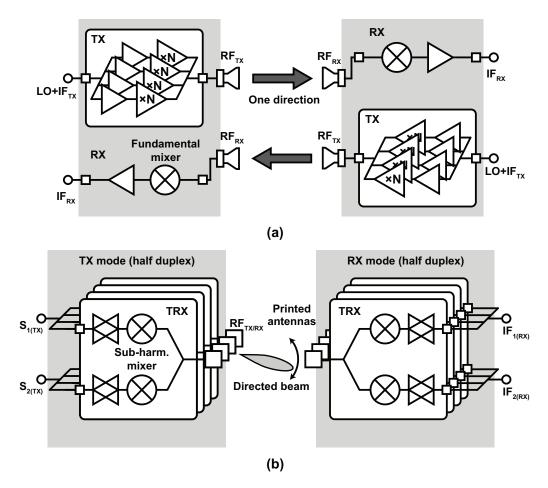

| 5.1  | (a) Conventional sub-THz transceiver (b) Proposed transceiver with bi-       |    |

|      | directional architecture and beamforming                                     | 66 |

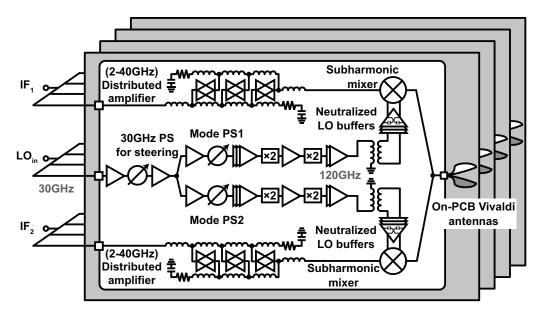

| 5.2  | Bi-directional 300GHz-band phased-array transceiver architecture             | 67 |

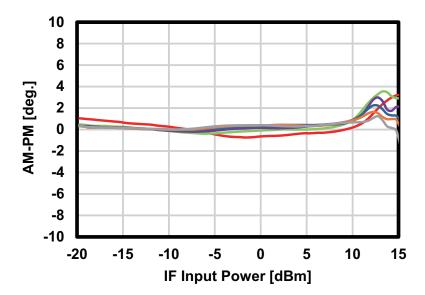

| 5.3  | Simulated AM-PM of the mixer for several frequencies (3GHz to 33GHz          |    |

|      | with 6GHz step)                                                              | 68 |

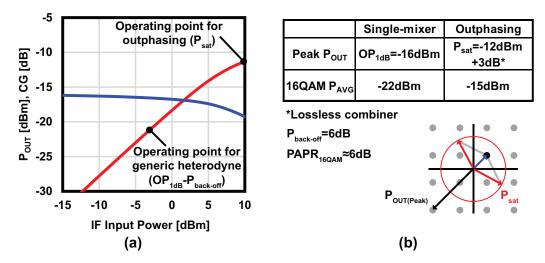

| 5.4  | (a) Mixer simulated characteristics and operating point options. (b) Im-     |    |

|      | provement on average power by outphasing                                     | 69 |

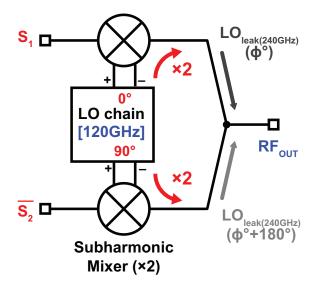

| 5.5  | LOFT cancellation technique                                                  | 69 |

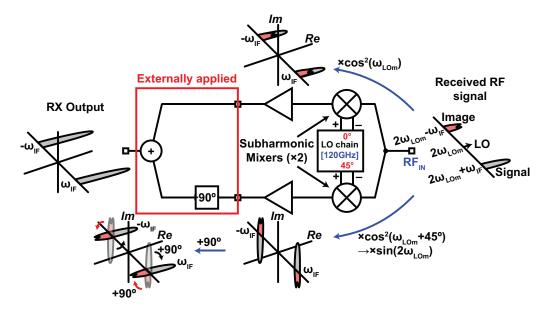

| 5.6  | The operation of the Hartley receiving mode                                  | 71 |

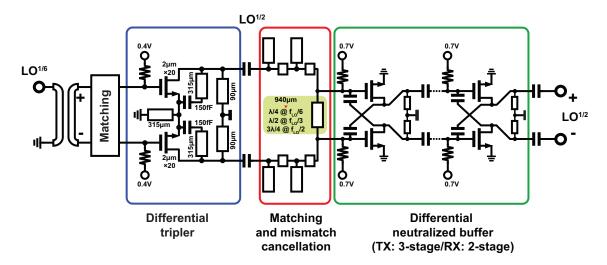

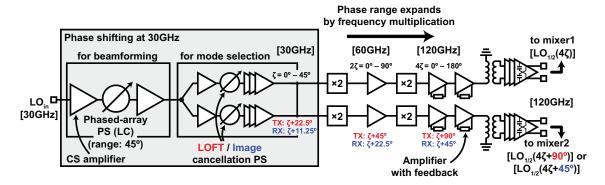

| 5.7  | LO chain block diagram                                                       | 72 |

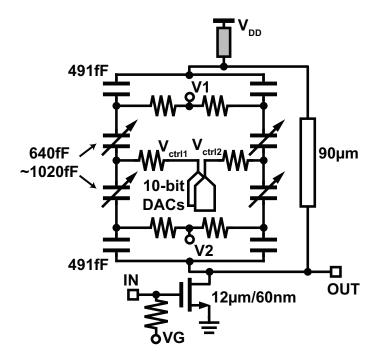

| 5.8  | Phase shifter core schematic                                                 | 73 |

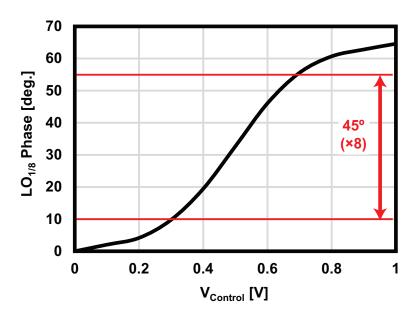

| 5.9  | Phase shifter measured phase range                                           | 73 |

| 5.10 | (a) Frequency doubler schematic and simulated output power, (b) Simu-        |    |

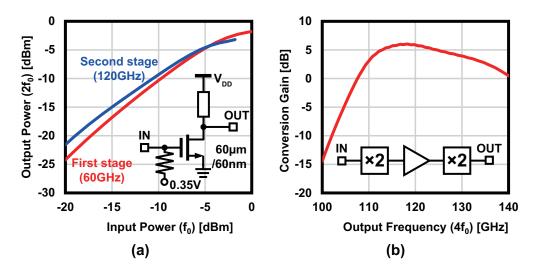

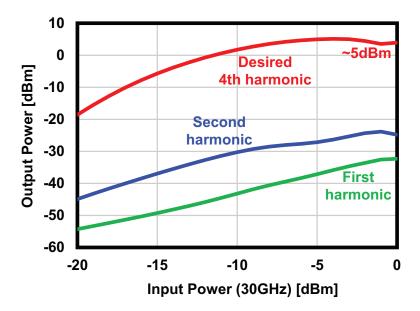

|      | lated conversion gain of the quadrupler chain                                | 74 |

| 5.11 | Schematic of the two-stage 120GHz single-ended LO Buffer using the           |    |

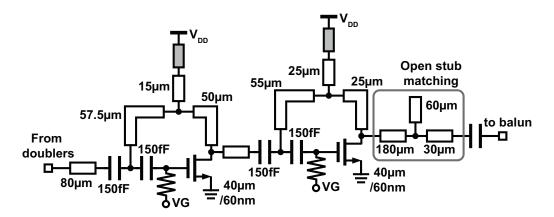

|      | maximum achievable gain                                                      | 75 |

| 5.12 | The simulated output power of the single-ended LO chain (balun input)        | 76 |

| 5.13 | (a) Differential LO buffer schematic                                         | 76 |

| 5.14 | Differential neutralized LO buffer chain output power characteristics (mixer |    |

|      | LO input power)                                                              | 77 |

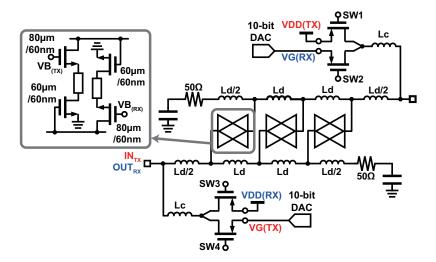

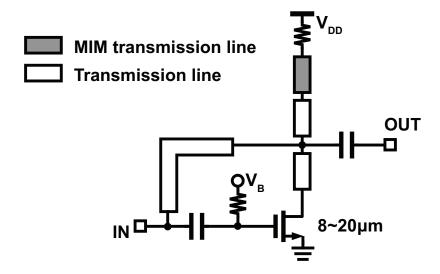

| 5.15 | Bi-directional distributed variable-gain IF amplifier schematic              | 77 |

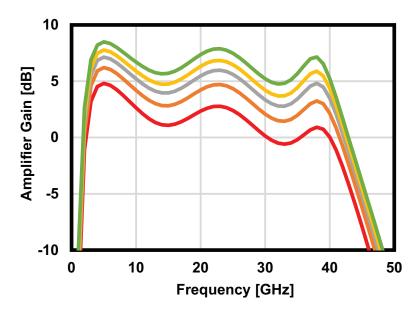

| 5.16 | IF amplifier simulated gain for several voltages                             | 78 |

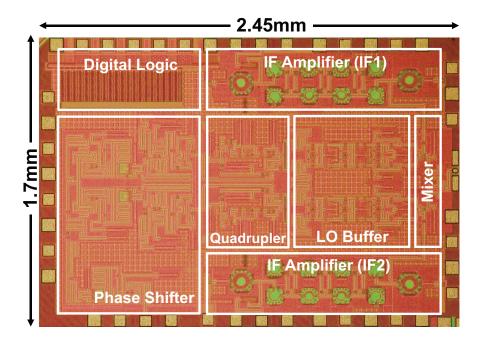

| 5.17 | The die micrograph. (© 2021 IEEE)                                            | 78 |

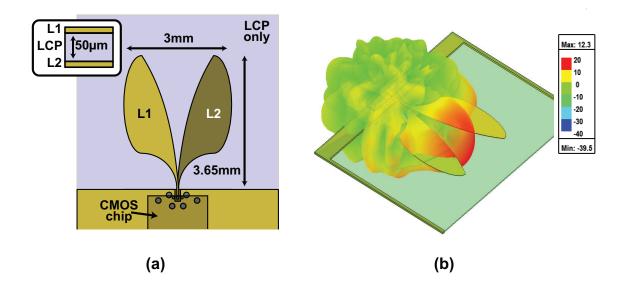

| 5.18 | Vivaldi antenna (a) design, (b) simulated 3D pattern                         | 79 |

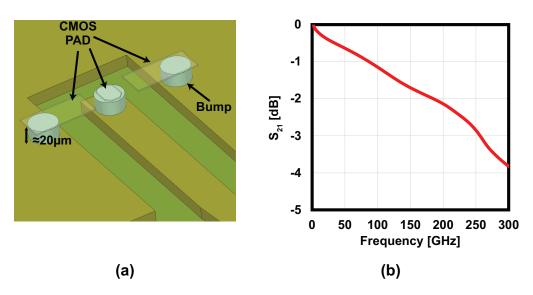

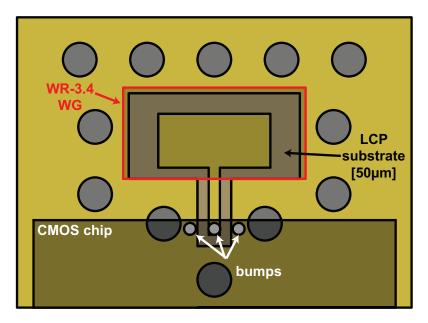

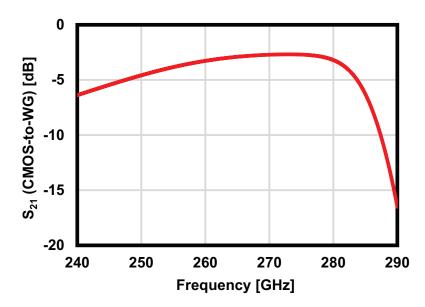

| 5.19 | Bump connection between the CMOS and the LCP PCB (a) model and               |    |

|      | (b) simulated loss                                                           | 80 |

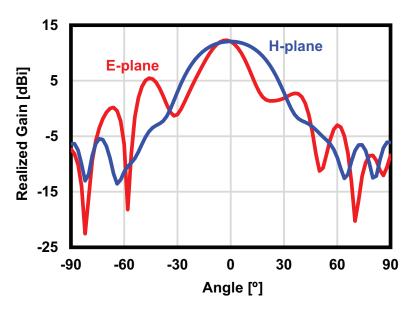

| 5.20 | Vivaldi antenna simulated realized gain (including the connection to CMOS).  | 80 |

| 5.21 | Vivaldi antenna simulated realized gain in the E-plane and the H-plane       |    |

|      | (including the connection to CMOS)                                           | 81 |

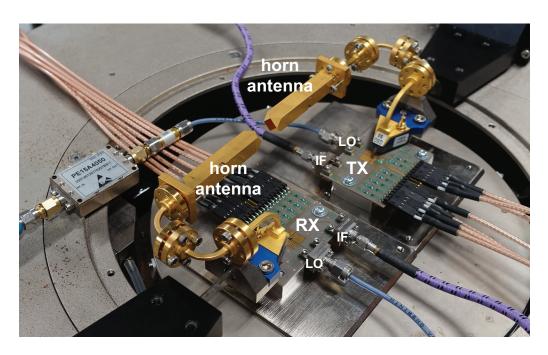

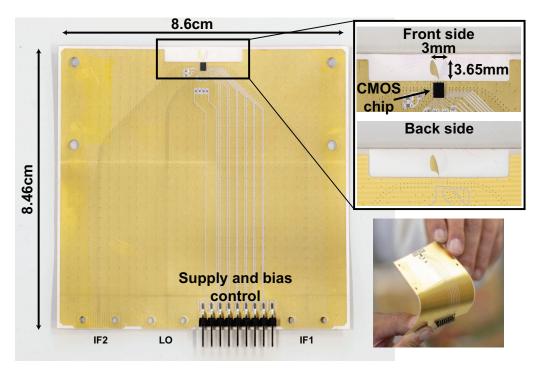

| 5.22 | Photographs of the PCBs used for phased-array implementation                 | 81 |

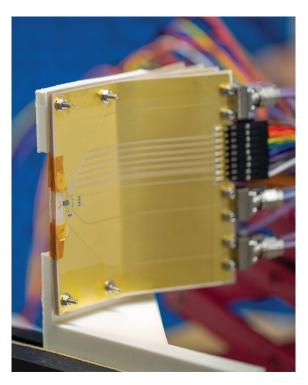

| 5.23 | A photograph of the implemented 4-element phased-array                       | 82 |

| 5.24 | CMOS-to-PCB transition design for PCB evaluation board                       | 83 |

| 5.25 | Evaluation board photo (The CMOS-to-PCB transition module installed).        | 83 |

| 5.26 | Simulated loss of the CMOS-to-WG transition                                  | 84 |

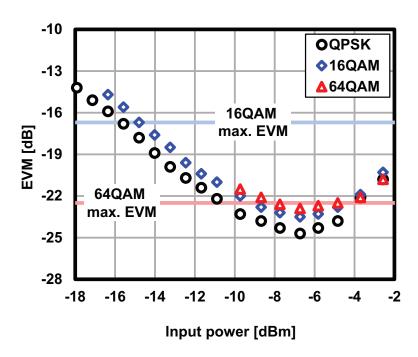

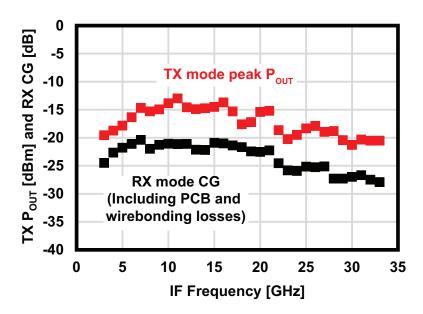

| 5.27 | Measured TX mode output power and RX mode conversion gain                    | 84 |

LIST OF FIGURES xiii

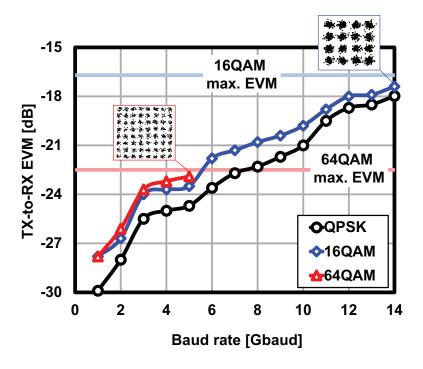

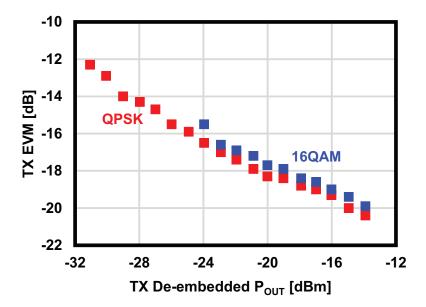

| 5.28 | Measured transmitter EVM                                                      | 85 |

|------|-------------------------------------------------------------------------------|----|

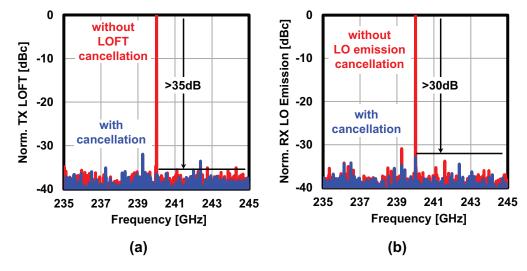

| 5.29 | Measured LOFT cancellation (a) in the TX mode and (b) the RX LO               |    |

|      | emission rejection mode                                                       | 85 |

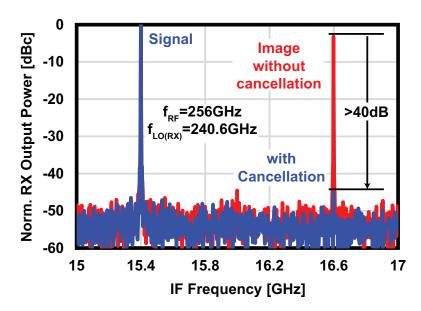

| 5.30 | Measured image rejection of RX Hartley mode                                   | 86 |

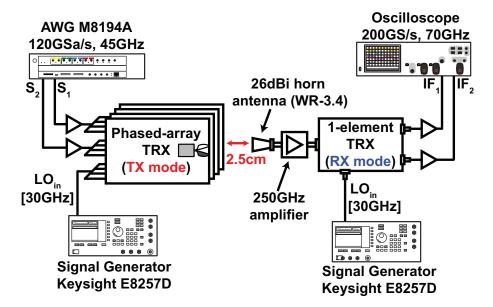

| 5.31 | Measurement setup for TX mode EVM                                             | 86 |

| 5.32 | Measurement setup for RX mode EVM                                             | 87 |

| 5.33 | Measured EVM and constellations of TX mode                                    | 87 |

| 5.34 | Measured EVM and constellations of RX mode                                    | 88 |

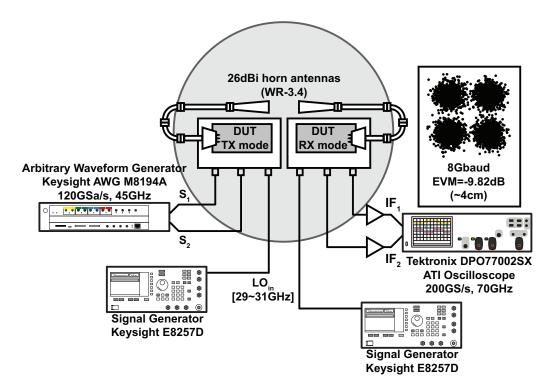

| 5.35 | Measurement setup of OTA measurement                                          | 89 |

| 5.36 | Array pattern measurement setup block diagram                                 | 90 |

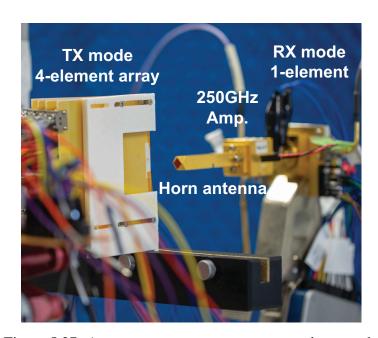

| 5.37 | Array pattern measurement setup photograph                                    | 90 |

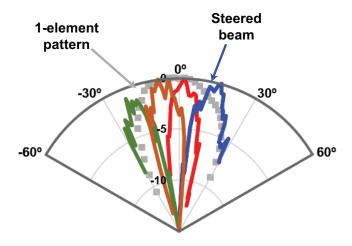

| 5.38 | Measured steered beam pattern                                                 | 91 |

| 6.1  | Potential 6G transceiver architecture options. (a) CMOS-only phased-          |    |

|      | array with dual-polarization. (b) Hybrid phased-array with dual-polarization. |    |

|      | (c) Full-duplex hybrid phased-array                                           | 95 |

| 6.2  | 300GHz-band CMOS amplifier circuit                                            | 96 |

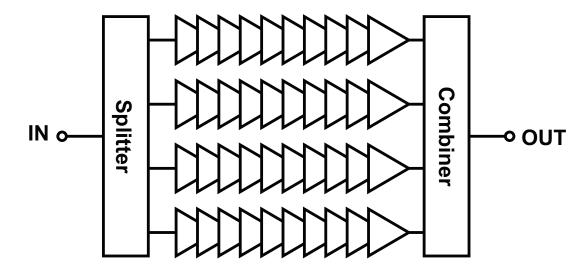

| 6.3  | Possible CMOS 300GHz-band power amplifier structure                           | 97 |

| 6.4  | Two-dimensional array implementation using stacked PCBs                       | 98 |

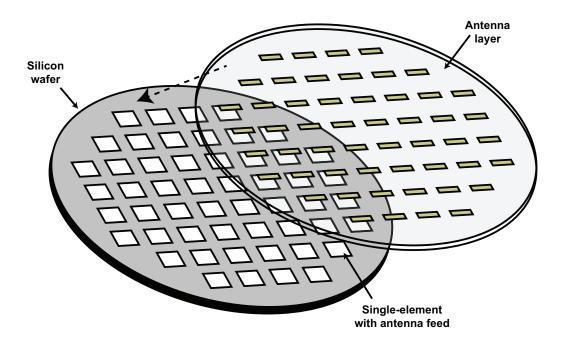

| 6.5  | Wafer-scale phased-array concept                                              | 99 |

## **List of Tables**

| 3.1 | Tripler Performance Comparison                                        | 27 |

|-----|-----------------------------------------------------------------------|----|

| 3.2 | Doubler Performance Comparison                                        | 38 |

| 4.1 | TX IF amplifier detailed parameters                                   | 47 |

| 4.2 | RX IF amplifier detailed parameters                                   | 48 |

| 4.3 | Power consumption of transmitter blocks                               | 56 |

| 4.4 | Power consumption of receiver blocks                                  | 56 |

| 4.5 | CMOS transceiver performance comparison                               | 56 |

| 4.6 | Hybrid transceiver performance comparison                             | 62 |

| 5.1 | Power consumption of transceiver blocks (single-element)              | 91 |

| 5.2 | Performance Comparison with State-of-the-Art 300GHz-band Transceivers | 92 |

## Chapter 1

## Introduction

We have been experiencing a massive evolution of the wireless communication technologies in the last 20 years due to the exponential growth of data consumption worldwide [1]. Every year, the communication technologies are becoming a more essential part of our lives as social media, e-commerce, live-streaming, and video download applications are seeing a rapid growth in the recent years. Being connected became much more vital after the global spread of COVID-19 as remote education and work was the only way to keep productive during quarantine. The start of 5G infrastructure deployment in the last couple of years is another sign that we are entering a new era of communications where being connected all the time is the norm. Mainly, Frequencies below 6GHz were used for communication systems due to the small path-loss and the relatively low-loss implementation options. However, these frequencies are crowded with many applications and the achievable data rate is quite limited. The 5G regulated by the 3rd Generation Partnership Project (3GPP) utilizes higher frequencies in the millimeter wave (mm-wave) bands to provide higher data rate links at the expense of shorter communication range. Phasedarrays are also essential for the operation of the 5G transceivers to overcome the increase of the path-loss. 5G systems are expected to reach data rates as high as 10Gb/s with low latency. Furthermore, 5G is targeted to be a technology that supports future industry and society, for use cases demanding particular requirements and high performance. The 5G technology will be set to a constant evolution in the next years to deal with the wide range of applications. In the recent years, a lot of efforts were made to implement high performance millimeter-wave transceivers for 5G and for the 60GHz standards as well [2-6].

Ten years from now, the next generation of wireless communications, which is going to be potentially called "6G", is anticipated to be introduced. After achieving many use cases and solutions for social issues by 5G, the fusion of several use cases and the needs

2 Introduction

Figure 1.1: 6G technology requirements.

Figure 1.2: 6G technology possible applications

for new use cases will appear. However, the combination of requirements of the new use cases cannot be covered by the 5G performance. Fig.1.1 shows the requirements that will be aimed for in the 6G technology [7]. More diverse and new requirements that are not fulfilled by the 5G and its evolution are considered with new use cases expected to appear after the deployment of 5G. Extremely higher data rates (>100Gb/s), low latency, wide coverage, low cost and energy, high reliability, and massive connectivity are the main requirements considered in the current vision for 6G.

Some of the applications that represent new use cases for 6G are shown in Fig.1.2. Using extremely high data rate wireless communication can provide solutions to the current bottlenecks [8]. In addition, light field and holographic displays demand hundreds of Gb/s communication speeds that cannot be satisfied by the 5G technology [9]. Uncom-

pressed video streaming and massive sensor networks are also among the applications that are still out of reach for the current technologies.

One of the driving factors of the emerging of 6G is that the 5G millimeter-wave frequency bands (e.g. 28GHz and 39GHz) do not have enough bandwidth to accommodate the speed and capacity requirements of the 6G use cases. Hence, higher frequency bands are being considered, especially in the sub-THz (0.1-1THz) region. High data rates were demonstrated using transceivers operating around 100GHz [10–15], but the lack of standardization and the existing regulations and applications make it difficult to realize the same data rates when actual deployment is considered. On the other hand, one of the most appealing candidates to be utilized in 6G is the 300GHz-band which roughly covers the frequencies from 250GHz to 320GHz. The 300GHz-band has three main characteristics that make it a very desirable choice for some 6G applications: (i) the available bandwidth is very wide with much less crowdedness compared to the lower frequency bands, (ii) electronic devices can still operate at this band with acceptable performance compared to the higher frequencies, and finally (iii) the short wavelength at 300GHzband which enables miniature antenna implementation with an order of several hundred  $\mu$ m. The 300GHz phased-array technology that is introduced in the following chapters is expected to be one of the key enabling technologies for 6G as it makes it possible to satisfy the data rate and latency requirements. Other 6G enabling technologies also include non-Terrestrial Networks for wide coverage, wireless power transfer for low energy solutions and massive connectivity, and new network topologies.

In this thesis, the design of a future 6G 300GHz-band wireless transceiver system is studied. Leveraging the advantages of the 300GHz-band requires special design considerations to overcome its big challenges such as the high path loss (around 20dB more than the 5G bands), the high component losses, the limited performance of the main system components, and other challenges that will be mentioned later in this thesis.

#### 1.1 Standards and Regulations for 300GHz-band

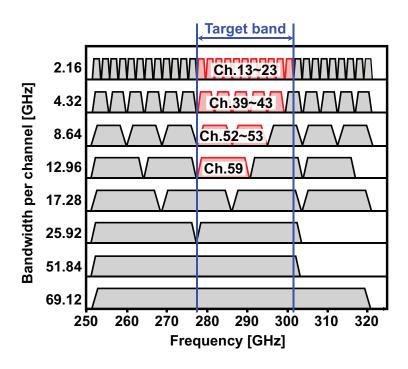

As the 300GHz-band is starting to attract attention recently, efforts have been made to standardize this band. The Institute of Electrical and Electronics Engineers (IEEE) introduced IEEE Std. 802.15.3d–2017 which is an amendment of the IEEE Std. 802.15.3d–2016 to define a wireless PHY layer that operates at 100Gb/s [16]. The standard covers the frequencies between 252.72GHz and 321.84GHz. 69 channels with 8 supported bandwidths from 2.16GHz and up to 69.12GHz which is quite massive and should easily fulfill the requirements of 6G new use cases. The standard channels are shown in Fig.1.3.

According to the decisions at the World Radio Conference 2019 (WRC-2019), the

4 Introduction

Figure 1.3: IEEE Std. 802.15.3 channel plan.

mentioned standard bands can be used for THz communications, but the radio astronomy and satellite services must be protected [17]. The bands 275-296GHz, 306-313GHz, 318-333GHz, and 356-450GHz have no specific conditions to protect Earth exploration and satellite service applications [18, 19], so a very wide bandwidth is still available to use without potential interference concerns.

The standards and regulations of the 300GHz-band may keep getting updated in the coming years based on the interference analysis and the new challenges to appear before the deployment.

## 1.2 300GHz-band CMOS Transceivers

Many works have utilized the 300GHz-band to achieve high data rates up to 120Gb/s using compound semiconductors or SiGe as in [20–33]. The high  $f_{\rm max}$  makes it possible to design power amplifiers (PA) and low noise amplifiers (LNA) with high gain and good linearity resulting in an excellent EVM performance. However, the compound semiconductor process-based systems are costly, very difficult to integrate, and large-scale digital circuits are not feasible in most cases, reducing the system's overall feasibility. The CMOS process is still more desirable as the main system process due to its low cost, excellent area efficiency, and high integration ability. Implementing the whole transceiver system using CMOS process means that both the RF front-end, the A/D and D/A inter-

Figure 1.4: Generic architecture for the 300GHz-band transceiver.

faces, the control/calibration circuits, and the processing circuits can be all integrated on one chip. System-on-chip (SoC) which is very common in mobile devices can also be realized by the full-CMOS implementation. However, there are many design difficulties that must be faced to make the operation of the transceiver acceptable. One large drawback of the CMOS process is its low  $f_{\text{max}}$  which does not normally exceed 300GHz. As a result, the RF-side amplifiers (PA and LNA) are not feasible so far, causing the dominance of the mixer-last (frequency-converter-last) TX, mixer-first RX architecture in the recent works [34–47]. For transceiver systems with amplifiers, lower frequencies were used as in [10, 48–50]. The mixer-last TX mixer-first RX architecture suffers from the limited linearity, high noise figure, and LOFT radiation from both the TX and the RX (LO emission). Fig.1.4 shows the general architecture of a heterodyne 300GHz-band mixer-last TX mixer-first RX transceiver. Besides the challenging mixer design, the LO generation circuit design is also very critical considering the very high operation frequency. The CMOS-based transceivers usually utilize LO frequencies in the D-band (110–170GHz) to realize LO buffering with decent driving power to be applied to the mixer. Several up-conversion steps and/or subharmonic mixing are the main techniques used to reduce the LO frequency. Consequently, frequency multiplier design in the D-band is very crucial to achieve the required performance of the LO chain. Additionally, circuit-level and architecture-level novel techniques are essential for the wireless link to be realized.

#### 1.3 Overview of This Thesis

The main aim of this thesis is to study the 300GHz-band transceiver implemented using CMOS process and to develop techniques for achieving wireless communication while

6 Introduction

keeping the power consumption to an acceptable value. PCB implementation for simple transceivers and phased-array transceivers is also considered.

This thesis is organized as follows: Chapter 2 introduces the main concepts and challenges that face the design of 300GHz-band CMOS circuits and transceivers. In this chapter, the most important challenges and requirements of the transceiver systems are discussed. The CMOS transistor limitations at high frequencies, LO chain and mixer requirements are explored. Beamforming importance and realization conditions are alos explained in this chapter.

Chapter 3 presents several frequency multiplier topologies for F-band and D-band LO signal generation with high output power, low power consumption, and harmonic suppression. Both single-ended and differential solutions are considered.

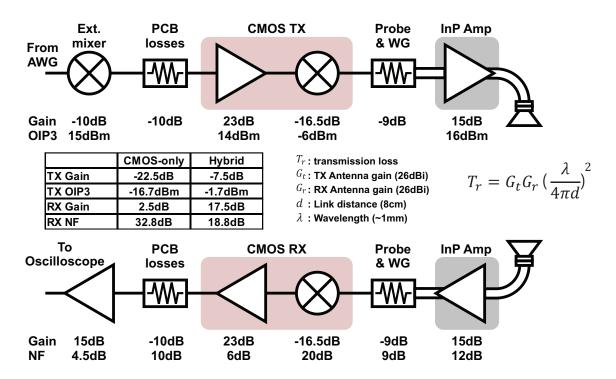

Chapter 4 presents a 300GHz-band CMOS transceiver system based on subharmonic mixing architecture. The system presented in this chapter achieves 300GHz wireless communication while consuming lower DC power than the recent designs. A subharmonic mixer with high conversion gain and acceptable linearity is presented in this chapter. A hybrid transceiver architecture that includes both CMOS up-/down-conversion circuitry and InP amplification circuitry is also presented in this chapter to study the alternative solutions for high performance 300GHz links.

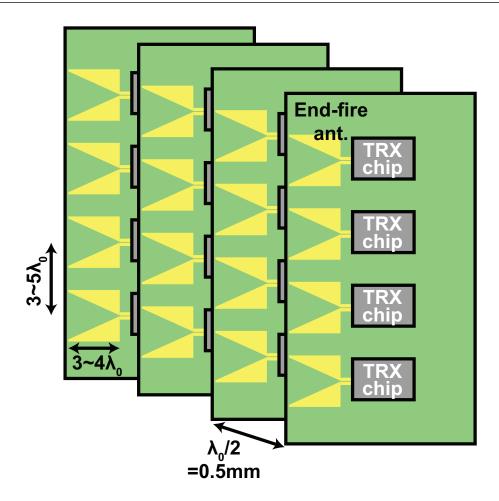

Chapter 5 presents a 300GHz-band CMOS bi-directional phased-array transceiver system that provides critical features for millimeter-wave links such as beamforming. Output power improvement and image rejection techniques which are included in the system are also explained in this chapter. This chapter also explores the possible phased-array architectures for 300GHz-band systems and explains the details of the stacked antenna solution.

Finally, the conclusions and future directions of this research are presented in chapter 6.

## **Chapter 2**

# 300GHz-Band CMOS Phased-Array Design Challenges

As discussed in the previous chapter, realizing a 300GHz-band wireless link using the CMOS process is very challenging and requires taking many factors into consideration. This chapter explains in detail the main obstacles and challenges that face the implementation of a practical 300GHz-band CMOS transceiver system with an acceptable power consumption and manufacturing cost.

## 2.1 $f_{\text{max}}$ of the CMOS Transistor

One of the most important parameters used to evaluate the transistor performance at millimeter-wave and sub-THz frequencies is the maximum oscillation frequency ( $f_{max}$ ).  $f_{max}$  is the frequency at which the maximum available gain becomes 1 and is the maximum frequency the transistor can oscillate at. Beyond that frequency, it is not possible to achieve any gain from the transistor. To determine the value of  $f_{max}$  for a transistor using the S-parameters, the maximum available gain ( $G_{a(max)}$ ) or MAG) is calculated first. MAG is the theoretical gain achieved when the input and the output impedances of the transistor are perfectly matched. It can be calculated as:

$$G_{\text{a(max)}} = \frac{|S_{21}|}{|S_{12}|} \left( K - \sqrt{K^2 - 1} \right)$$

(2.1)

where  $S_{ij}$  are the s-parameters of the transistor, and K is the stability factor which is calculated as follows:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |D|^2}{2|S_{12}S_{21}|}$$

(2.2)

Figure 2.1: Simulated maximum available/stable gain for several transistor sizes in 65nm CMOS process.

given that

$$D = S_{11}S_{22} - S_{12}S_{21} \tag{2.3}$$

This definition of MAG is only applicable when the device is stable unconditionally (K > I), which is the case at higher frequencies. When the device is conditionally stable (K < I), the maximum stable gain (MSG) is used and it is defined as:

$$G_{\text{s(max)}} = \frac{|S_{21}|}{|S_{12}|} \tag{2.4}$$

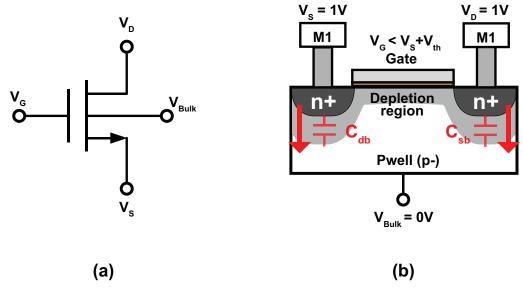

Fig.2.1 shows the simulated MAG/MSG for several transistor sizes in CMOS 65nm process. The frequency at which the MAG becomes 1 (0dB) is the  $f_{\rm max}$ . Beyond that frequency, it is not possible to achieve any gain from the transistor. It can be observed that the  $f_{\rm max}$  is less than 300GHz making it extremely difficult to implement a reliable amplifier circuit.

The  $f_{\text{max}}$  is also closely related to the parasitics of the transistor and its interconnects. The following formula clarifies the effect of the main parasitics on the  $f_{\text{max}}$  [51, 52]:

$$f_{\text{max}} = \frac{f_{\text{T}}}{2\sqrt{R_{\text{g}}g_{\text{m}}C_{\text{gd}}/(C_{\text{gs}} + C_{\text{gd}}) + (R_{\text{g}} + r_{\text{ch}} + R_{\text{s}})g_{\text{ds}}}}$$

(2.5)

Figure 2.2: Possible 300GHz-band system architecture options for different LO frequencies. (a) Simple fundamental mixing. (b) Both LO and IF are in the D-band. (c) Subharmonic mixing.

where  $f_{\rm T} = g_{\rm m}/2\pi(C_{\rm gs}+C_{\rm gd})$  is the cut-off frequency,  $R_{\rm g}$  and  $R_{\rm s}$  are the gate resistance and the source resistance, respectively.  $r_{\rm ch}$  is the equivalent non-quasi static resistance,  $g_{\rm ds}$  is the drain-source conductance,  $C_{\rm gd}$  is the gate-drain capacitance, and  $C_{\rm gs}$  is the gate-source capacitance.

It is clear from (2.5) that the  $f_{\text{max}}$  degrades as the parasitic resistance and capacitance increase. The gate resistance has the largest effect, so careful optimization of the gate connection can be one way to improve the overall frequency characteristics of the transistor. Also, (2.5) explains the reason behind the better performance of the smallest transistor in Fig.2.1 at high frequency compared to the larger ones. As a result, even when amplification is realized around 300GHz using CMOS transistors by applying suitable optimization to the transistor size and layout, the achieved output power will be low due to the small transistor size as in [53, 54] for example.

Taking the points mentioned above into consideration, the work in this thesis adopts the mixer-last TX mixer-first RX architecture to overcome the  $f_{\rm max}$  limitations. However,  $f_{\rm max}$  and gain improvement techniques are applied to the LO buffering circuits which operate between 100GHz and 150GHz as will be explained in the later chapters.

#### 2.2 LO Generation

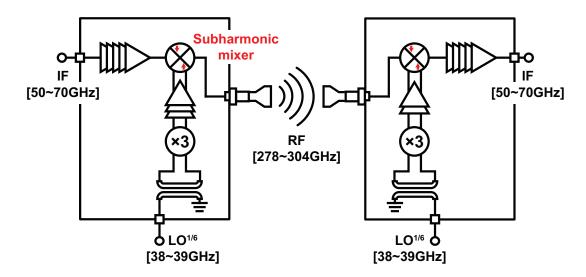

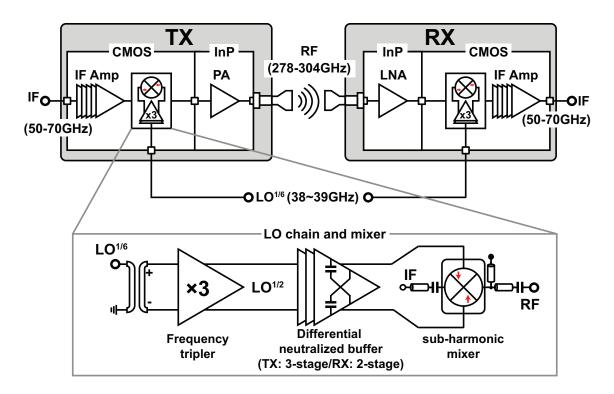

As mentioned in Chapter 1, the LO signal generation chain of 300GHz-band systems is a very critical part, and it decides how well the mixer operates by providing the suitable driving power and the suppression of the undesired harmonics. The frequency of the LO signal is decided depending on the system overall architecture, but because the RF frequency is extremely high, it is quite difficult to reduce the LO frequency to less than 100GHz. Fig2.2 illustrates several system architecture options that have been demonstrated in the literature (showing only the transmitter part). The simple fundamental mixing option in Fig2.2(a) is the most challenging to implement due to the high LO frequency as the <100GHz IF signal is supposed to be directly up-converted to a much higher frequency band. This option is rarely used due to the complex and power consuming LO generation circuit required to provide a suitable driving power using CMOS. The second option in Fig2.2(b) assumes an IF signal up-converted first to the D-band before getting up-converted again by the RF mixer. This option requires much lower LO frequency, and hence, a much simpler and less power consuming LO chain circuitry. The main issue in this option is the high IF signal frequencies in the D-band which are also required to occupy a very wide bandwidth as well. Implementing a reliable wideband CMOS amplifier that operates with suitable linearity characteristics at such frequencies is not straight forward, and the amplifier may cause the overall system linearity to degrade due to the poor CMOS gain performance in the D-band. Instead of increasing the IF frequency to such high frequencies, subharmonic mixing can be used as illustrated in Fig.2.2(c). The LO signal frequency is kept at around half the RF frequency in the D-band, and the IF frequency is set somewhere below 100GHz. This enables wideband IF amplification with decent linearity while utilizing a high power LO chain that consumes acceptable DC power.

The architecture in Fig.2.2(c) is adopted in all systems presented in this thesis due to its compatibility with the CMOS process. However, a subharmonic mixer with good linearity and high conversion gain is required to make the transceiver system feasible as will be shown in the later chapters.

Another issue that is related to the LO chain of 300GHz-band systems is the appearance of undesired harmonics at the output. Due to the frequency multiplication, many undesired harmonics appear at the output of the LO chain. These harmonics may upconvert undesired signals to the RF band, and they may cause serious linearity issues to the RF mixer. A detailed discussion about the requirements and the design techniques of the frequency multipliers is introduced in the next chapter.

### 2.3 Error Vector Magnitude

Bit Error Rate (BER) is one of the most common indicators to evaluate the communication system performance. It is the ratio between the number of bit errors and the total number of transmitted bits during a time interval. For wireless communication to take place, a BER of  $10^{-3}$  is considered acceptable. The BER is directly related to two other parameters that can be calculated directly from circuit component characteristics; signal-to-noise ratio (SNR) and error vector magnitude (EVM). Both of these parameters are closely related to each other as well, and the following equation estimates the that relation as calculated in [55]:

$$SNR \approx \frac{1}{EVM^2}$$

(2.6)

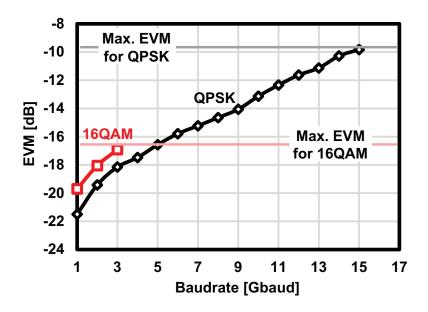

Fig.2.3 plots the relation between BER and SNR for several modulation schemes. As can be expected, higher SNR values are required for higher-order modulation schemes to achieve the required BER as the number of levels increases. A 9.8dB SNR (around -9.8dB EVM) is required to achieve QPSK wireless communication, while a 16.5dB (around -16.5dB EVM) SNR is required to achieve 16-QAM link and so forth.

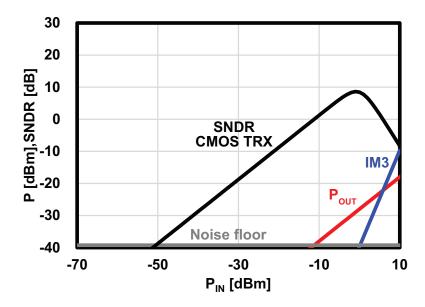

In the real case, there are many additional factors that increase the EVM and degrade the overall BER. The distortion caused by the non-linearity of the devices must be added to the equation by replacing the SNR by signal-to-noise and distortion ratio (SNDR), where the distortion is usually dominated by the third-order inter-modulation components (IM3). Additional EVM degradation factors including carrier phase noise ( $\varphi_{RMS}^2$ ), image signals or I/Q mismatch, LO feedthrough (LOFT) if in-band, and the gain flatness (GF) of the RF band. The equation (2.6) becomes as follows [5]:

$$EVM_{tot} \approx \sqrt{\frac{1}{SNDR^2} + \varphi_{RMS}^2 + EVM_{image}^2 + EVM_{LOFT}^2 + EVM_{GF}^2}$$

(2.7)

Achieving the EVM requirements for the 300GHz-band transceivers is much more difficult compared to the commonly used lower frequency bands as the target bandwidth is much wider, the path loss is much higher, and the device performance is quite limited. That explains the critical role of the RF mixers in the 300GHz-band CMOS mixer-last TX mixer-first RX systems, as the mixer characteristics define the overall EVM of the system. Here, both the output signal power and the noise figure of the mixer have direct effect on the system SNDR due to the absence of RF amplification.

Figure 2.3: Calculated BER against SNR for several modulation schemes

## 2.4 FSPL and Beamforming

The transmitted signal in any wireless system experiences a drop in its power level before reaching the receiver input due to the propagation nature of electromagnetic waves and the finite antenna size. This loss is commonly referred to as free-space-path-loss (FSPL) and is defined as follows:

$$FSPL(dB) = 20\log\left(\frac{4\pi df}{c}\right)$$

(2.8)

where d is the communication distance between the transmitter and the receiver, f is the signal frequency, and c is the speed of light. It is observed in (2.8) that increasing the frequency from the commonly used 3GHz frequency to 300GHz increases the FSPL by a huge 40dB (or 10000 times as can be expected from the inverse-square law). Antennas with high directivity such as horn antennas and lens antennas are commonly used to solve the large FSPL issue in 300GHz-band systems. However, such implementation causes the link to be realized only when the RX is placed within the radiation angle of the horn/lens antenna which is usually very narrow especially when the antenna gain gets higher. Any change of the RX radial position will highly degrade the communication performance.

To solve this issue effectively, many millimeter-wave systems adopt the phased-array implementation where many transceivers and their antennas (printed antennas in most cases) are placed as an array with certain pitch, and the phase of each transceiver (element) is controlled so that the total radiation direction shifts to the desired angle. This way, both

TX and RX radial positions can be changed within the range of the array which is much wider than the beam width of a high-gain horn antenna. Although the antenna gain of printed antennas is smaller than that of horn and lens antennas, the array gain itself gets higher as the number of elements increases. The following equation shows the calculation process of the link budget considering all parameters (all in dB):

$$P_{\text{OUT(TX)}} + G_{\text{TX}} + G_{\text{RX}} - FSPL - NoiseFloor > SNR_{\text{reg}}$$

(2.9)

where  $P_{\text{OUT(TX)}}$  is the output power of the TX,  $G_{\text{TX}}$  and  $G_{\text{RX}}$  are the antenna gain values of TX and RX, respectively (array gain if phased-array), NoiseFloor is the noise floor at the input of the receiver, and  $SNR_{\text{req}}$  is the required SNR for the target link.

Implementing the phased-array system at 300GHz-band has a big obstacle compared to the phased-array systems of lower millimeter-wave frequencies due to the very short wavelength. This issue is discussed in details in the next section.

#### 2.5 Challenges for 300GHz-band Phased-Array

The phased-array implementation is essential for 300GHz-band systems to overcome the high FSPL issue while providing some flexibility to the system so that additional applications and use cases become feasible for 6G technology in the future. However, the phased-array design at this band has many critical issues that are not considered dominant at lower frequencies. The first issue resides in the large losses that the passive structures have on- and off-chip due to the short wavelength of the target band. That means that antenna implementation and its connection to the transceiver circuit needs much more attention compared to the other bands. Another issue that is related to the physical structure of the array, especially the antenna spacing, is the very short antenna pitch required to achieve acceptable beam steering range. Other issues also include the area and cost limitations, and the power consumption. In this section, some more details about the mentioned issues are introduced, with a brief explanation of the strategies this thesis proposes to face them.

#### 2.5.1 Antenna Implementation and Connection

The short wavelength at 300GHz (around 1mm) reduces the size of the antenna considerably. This can be an advantage when wireless sensor networks or medical applications are targeted considering the size limitations in these cases. As the antenna size is in the millimeter order, it can be implemented even on-chip alongside the transceiver circuit.

However, the on-chip antenna characteristics rely heavily on the chip dielectric material characteristics, especially the relative permittivity ( $\varepsilon_r$ ) and the resistivity. The low resistivity of the silicon substrate for example causes large losses and a huge degradation in the radiation efficiency [56].

The on-PCB antenna is a better option when the antenna performance is prioritized. There are many PCB material choices with much better characteristics for antenna implementation. Low permittivity and higher resistivity can be obtained by using the suitable material regardless of the chip materials. The main drawback of the on-PCB antenna is that a lossy structure is required to connect the transceiver chip to the PCB antenna. Wire bonding is a very poor option at 300GHz considering its length which is too long compared to the wavelength, resulting in a large inductance that causes serious degradation to the RF signal. The flip chip process is another option that shows a much better compatibility with the higher frequencies due to the small size of the connecting bump. The distance between the chip and the PCB after implementation can be as short as  $20\mu$ m. On the other hand, the flip chip process is more complicated and costly compared to the wire bonding, and smaller bumps should be used at high frequency causing more complication and high cost.

#### 2.5.2 Antenna Placement and Spacing

The placement of antennas in phased-array systems must be considered thoroughly to avoid the degradation in the beam shape and the steering range. The spacing between antenna elements directly affect the angle range as can be calculated using the following equation:

$$\Delta \Phi = \frac{2\pi d \sin\theta}{\lambda} \tag{2.10}$$

where  $\Delta \Phi$  is the phase shift between elements, d is the distance between elements, and  $\theta$  is the beam angle. The beam angle range calculated results for three different antenna pitches  $(0.5\lambda, \lambda, \text{ and } 2\lambda)$  are shown in Fig.2.4. It can be observed that a long pitch causes the steering range to be narrower, and  $0.5\lambda$  is the maximum pitch that covers the whole range. A  $2\lambda$  pitch means that the steering range does not exceed 30° as well.

In the conventional millimeter-wave phased-array systems, the arrays consisting of broadside antennas like metal patches are more common as the antennas are aligned in a two-dimensional fashion with a  $\lambda/2$  pitch. For frequencies around 28GHz (5G standard band) this structure is not so difficult to realize as the wavelength is in the centimeter order as can be seen in Fig.2.5(a). However, when it comes to the 300GHz-band, the wavelength is much shorter, and the required pitch becomes shorter as well. Considering a 1–2mm wide chip, antennas need to be placed so far from chip to obtain the  $\lambda/2$  pitch as

Figure 2.4: Beam steering range for different antenna pitch lengths.

illustrated in Fig.2.5(b). The long distance between the chip and the antenna means that long lossy transmission lines are required on-PCB, causing huge losses to the RF signal.

On-chip arrays as in [57–61] make it possible to build a suitable structure with a suitable antenna pitch, but the chip area is huge and the antenna gain is limited due to the large silicon substrate loss as discussed in the previous section.

By knowing that the thickness of the CMOS chip with the PCB is still less than  $\lambda$  even at the 300GHz-band. A stacked antenna alignment can be adopted instead of the horizontally adjacent configuration as illustrated in Fig.2.5(c). The end-fire antennas are used here, and the antenna pitch in the stack can be  $\lambda/2$  without using long lossy connecting transmission lines.

#### 2.5.3 Power Consumption

The use of multiple transceiver circuits to build the phased-array system causes the overall power consumption to increase considerably. Hence, the power consumption of every chip must be minimized by improving the efficiency of the frequency conversion circuits.

#### 2.5.4 Manufacturing Cost

The manufacturing cost is another critical factor that must be considered in the phased-array system design. The chip area is surely one of the main cost deciders, but the off-chip connections are also very crucial at 300GHz. High-cost materials with good high

Figure 2.5: Phased-array implementation issue at 300GHz-band. (a) 28GHz phased-array structure. (b) Using the same structure for 300GHz. (c) Proposed stacked architecture.

frequency characteristics are required instead of the conventional cheap ones. Flip chip and module implementation also cause the cost of manufacturing to go up.

Another big choice to make for phased-arrays is whether to implement several transceivers on the same chip or to implement each transceiver on a chip. The first option reduces the off-chip components and losses, but higher chip fabrication cost is expected as the yield by necessity gets lower on bigger chips [62]. Such dilemmas and their solutions will shape the way sub-THz phased-array transceivers develop in the future.

## **Chapter 3**

## Frequency Multipliers for LO Generation <sup>1</sup>

The LO signal generation circuitry is one of the most challenging parts of the 300GHz-band systems as its operating frequency is in the sub-THz region, and the required output power is relatively high to drive the mixer properly. The low-efficiency LO buffers operating at the sub-THz frequencies consume large DC power as a result. So, if the previous frequency multiplier stage provides suitable signal power with sufficient undesired harmonic suppression, the number of LO buffering stages can be reduced lowering the overall system power consumption.

Simple circuit architecture is usually preferred at the sub-THz frequencies to reduce the losses and the required area as transmission lines are heavily used. So, relatively simple, high-power/conversion-gain characteristics, and fundamental/harmonic suppression are the main targets for sub-THz frequency multiplier design. In this chapter, several frequency multipliers operating mainly at the F-band (90-140GHz) frequencies with improved output power and harmonic rejection characteristics are introduced. The area is minimized by adopting very simple structures and effective rejection techniques.

#### 3.1 Frequency Multiplier Topologies

Many works focused on providing superior frequency multiplier circuits at W-, F- and D-band as in [64–72]. The choice of the suitable frequency multiplier topology to be used

<sup>&</sup>lt;sup>1</sup>This chapter is based on "F-band Frequency Multipliers with Fundamental and Harmonic Rejection for Improved Conversion Gain and Output Power" [63], by the same author, which appeared in the IEICE Transactions on Electronics, © 2021 IEICE. The material in this paper was presented in part at the IEICE Transactions on Electronics [63], and some of the figures of this paper are reused from [63] under the permission of the IEICE.

Figure 3.1: Conventional frequency multiplier topologies: (a) Injection-lock-based, (b) Mixer-based, (c) Device nonlinearity-based, and (d) Push-push-based.

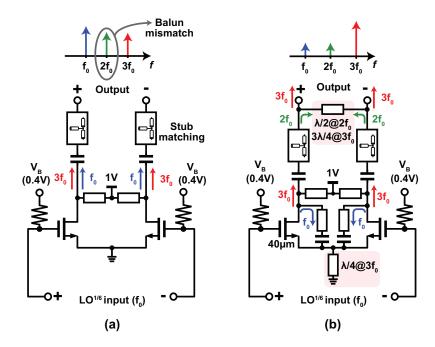

in the 300GHz-band CMOS transceiver system usually depends on the simplicity and the feasibility at frequencies around the f<sub>max</sub>. The main common frequency multiplier topologies can be divided into four as illustrated in Fig. 3.1 [73]. The injection-based topology [64] can provide the desired output with relatively low input power, but they have limited performance when operating at a frequency far from the center frequency. Mixer-based multipliers have a wider operation bandwidth, but they have high input requirements to operate properly [72]. Device/Line Nonlinearity-based multipliers [65, 68] are very common for high frequencies due to their simplicity and compatibility with the transmission line-based design. However, their conversion gain is limited and the undesired harmonics still appear at the output due to the wideband characteristics of the matching circuits at such frequencies. Push-push-based frequency doublers are also very common for sub-THz systems [66, 67, 69–71], but balun mismatches at the input side cause leakage of the fundamental signal to the output and degrades the output power.

In the following sections of this chapter, F-band device nonlinearity-based frequency triplers with fundamental and second harmonic cancellation techniques and a push-push-based frequency doubler with balun mismatch compensation techniques are introduced.

Figure 3.2: Conventional device nonlinearity-based frequency triplers: (a) Single-ended, (b) Differential with second harmonic resonance at the tail node.

## 3.2 Millimeter-Wave Frequency Triplers

One of the main design considerations of the frequency multiplier design is the ability to reject undesired harmonics so that they do not appear at the output. The devicenonlinearity-based frequency multipliers normally operate at higher input power values to get higher conversion gain. So, suppressing the fundamental frequency and the undesired harmonics is very important to avoid the saturation of the circuit by the undesired components. As a result, the desired frequency signal will dominate the output and its power will improve. For the frequency tripler circuit, the most common technique to reject the fundamental signal is by utilizing the bandpass characteristics of the output matching network. However, the wideband nature of the transmission-line-based matching networks causes the rejection to be insufficient. Placing open quarter-wave stubs at the output to reject the fundamental component is not effective for triplers because the third harmonic will face a small impedance similar to that at the fundamental frequency as the electrical length there is  $3\lambda/4$ . Using the quarter-wave stub at the second harmonic frequency also degrades the third harmonic output power due to the wideband characteristics of the stub. The conventional architecture is illustrated in Fig. 3.2,(a). One of the solutions is to use the differential architecture to automatically cancel the second harmonic which has even characteristics as shown in Fig. 3.2,(b). By adding a tail inductance, the output can be improved as well [34]. However, the fundamental rejection still depends on the matching network characteristics. It is also common to have single-ended buffering stages when it comes to the operation close to  $f_{\text{max}}$  due to the design flexibility and layout simplicity.

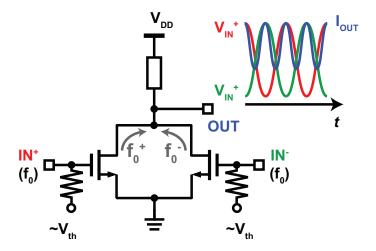

This section presents two novel tripler circuits for improved output power and harmonic rejection; (i) a single-ended tripler circuit with a passive feedback network, and (ii) a differential tripler with filtering stubs and balun mismatch compensation.

Figure 3.3: Proposed fundamental and second harmonic rejection technique. (a) The feedback network operation. (b) The circuit built using lumped components. (c) The proposed circuit.

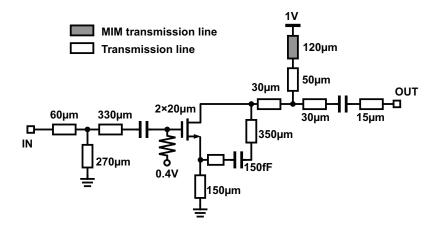

## 3.2.1 Proposed Single-Ended Tripler

In this work, a tripler circuit with a passive feedback network is proposed to improve the performance as shown in Fig. 3.3,(a). The inductor that is connected to the source resonates at the second harmonic to generate the cancellation signals, and the passive network passes these components to the output with the suitable phase shifts. The phase difference between the drain current and the feedback current at the undesired fundamental and second harmonic frequencies must be around 180° to provide the cancellation, while a phase difference of less than 90° between the drain and the feedback currents is required at the desired third harmonic to avoid any cancellation as:

$$|I_{\text{out3}}| = \sqrt{|I_{\text{d3}}|^2 + |I_{\text{f3}}|^2 + 2|I_{\text{d3}}||I_{\text{f3}}|\cos(\theta)}$$

(3.1)

Figure 3.4: (a) The inductance of the tail transmission line. (b) The voltage magnitude at the source for all the harmonics. ( $f_0$ =38GHz,  $P_{IN}$ =10dBm)

where  $I_{\text{out3}}$ ,  $I_{\text{d3}}$ , and  $I_{\text{f3}}$  are the output, drain, and feedback currents at the third harmonic, respectively.  $\theta$  is the phase differency between the drain and the feedback currents. For  $|\theta| \le 90^{\circ}$ , it is guaranteed that the output current is larger than the drain current. The passive network is also designed to have a very low impedance at the fundamental frequency to increase the suppression, and a very high impedance at the desired third harmonic to avoid any degradation.

The circuit can be designed using lumped elements as shown in Fig. 3.3,(b). However, using the inductors at high frequencies may cause some design difficulties regarding their modeling and layout limitations. Hence, in this work, we use the transmission lines to provide the suitable inductance and phase shifts as illustrated in Fig. 3.3,(c).

To calculate the source transmission line length, the input impedance formula is used:

$$Z_{\rm in}(l) = Z_0 \frac{Z_{\rm L} + j(Z_0 \tan(\frac{2\pi}{l}l))}{Z_0 + jZ_{\rm L} \tan(\frac{2\pi}{l}l)}$$

(3.2)

where  $Z_{in}(l)$  is the input impedance of the line with the transmission line length l,  $Z_0$  is the characteristic impedance of the transmission line (50  $\Omega$ ),  $\lambda$  is the electrical wavelength, and  $\omega$  is the angular frequency. For a  $Z_L = 0$ , the transmission line length to provide the suitable inductance is around 150 $\mu$ m. The simulated inductance is shown in Fig. 3.4(a). The voltage components at the transistor source are shown in Fig. 3.4(b) with the second harmonic voltage having the largest magnitude. The calculated value provides the best second harmonic rejection as the simulation results show in Fig. 3.5. The sensitivity of

Figure 3.5: Simulated output power of the frequency tripler for different tail transmission line lengths. ( $f_0$ =38GHz,  $P_{IN}$ =10dBm)

Figure 3.6: Simulated output power of the frequency tripler for different feedback transmission line lengths. ( $f_0$ =38GHz,  $P_{IN}$ =10dBm)

the operation against the feedback line variation is also investigated in Fig. 3.6 and the performance is reliable even for large line length error. Adding the transmission line to the source slightly degrades the small-signal output power of the tripler, but the improvement

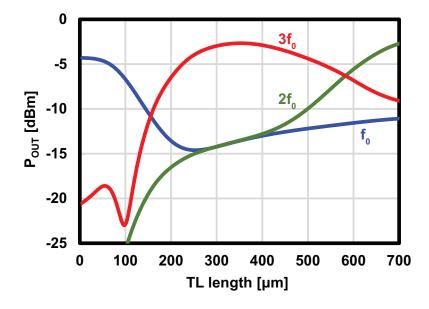

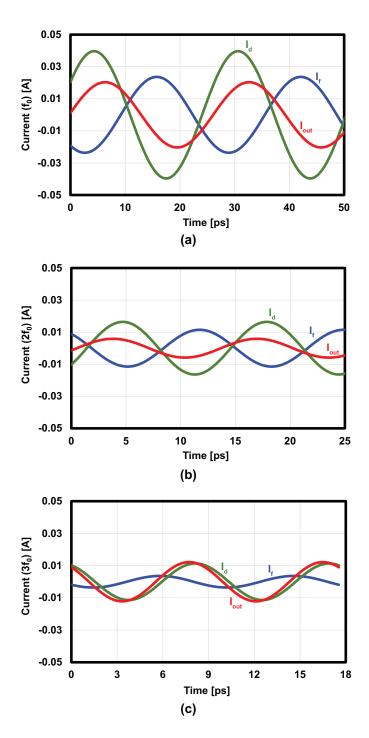

Figure 3.7: Frequency tripler simulated operation: (a) The simulated currents, (b) The simulated phase difference between the drain and the feedback currents. ( $f_0$ =38GHz,  $P_{IN}$ =10dBm)

caused by the fundamental and second harmonic rejection has a larger effect for higher input power situations.

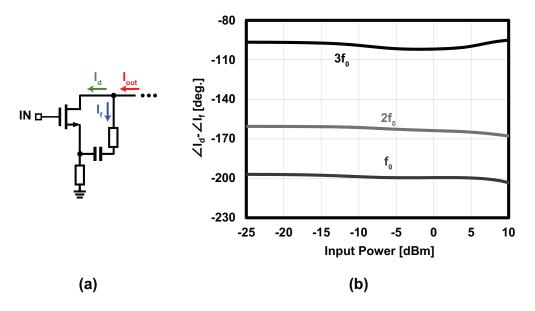

The operation of the tripler is further investigated in Fig. 3.7. The currents of the branches shown in Fig. 3.7(a) are simulated to evaluate the feedback performance. The simulated phase difference between the drain current and the feedback network current is near 180°, as shown in Fig. 3.7(b), and the difference is close to 90° in the third harmonic signal case. The output current is considerably smaller than the original drain current at the fundamental and the second harmonic frequencies as can be observed in Fig. 3.8(a) and (b). The output current at the fundamental frequency seems large at the output, but it can be easily suppressed further by the matching network as the desired frequency is much higher. The desired third harmonic signal amplitude has a slight increase due to the 90° phase difference (Fig. 3.8(c)).

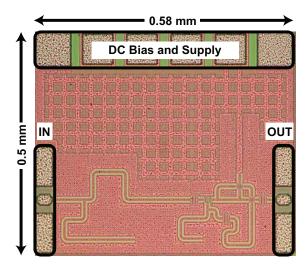

The detailed schematic of the proposed tripler is illustrated in Fig. 3.9. Input and output matching circuits are implemented using short stubs. The micrograph of the chip which was fabricated using 65nm CMOS is shown in Fig. 3.10. The simple, single-ended circuit structure made the area as small as 0.29mm<sup>2</sup> with a much smaller active area.

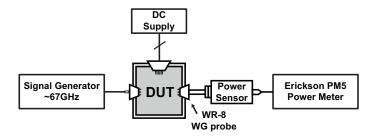

The measurement setup used to characterize the proposed tripler is illustrated in Fig. 3.11. The input signal is generated using a 67GHz signal generator that covers the whole target band, and the output is detected using VDI Erickson Power Meter. A WR-8 waveguide

Figure 3.8: Frequency tripler simulated operation: (a) Current waveforms of fundamental signals, (b) second harmonic signals, and (c) third harmonic signals ( $f_0$ =38GHz,  $P_{IN}$ =10dBm)

Figure 3.9: Proposed frequency tripler circuit schematic.

Figure 3.10: Frequency tripler micrograph. (© 2021 IEICE)

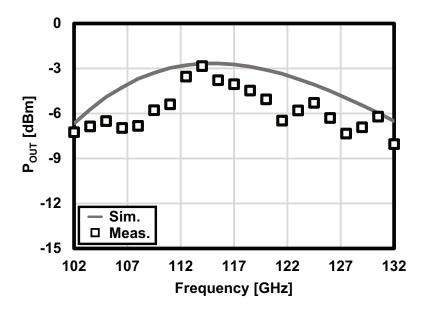

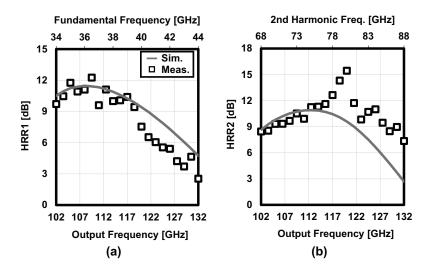

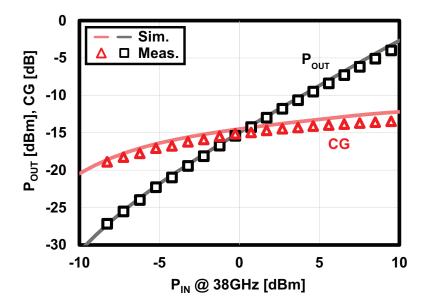

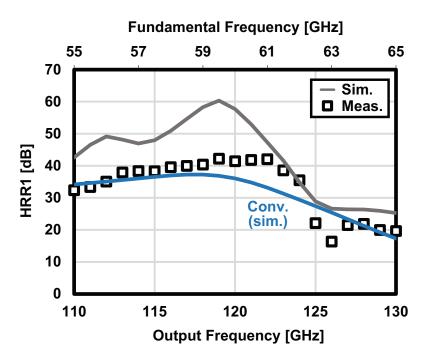

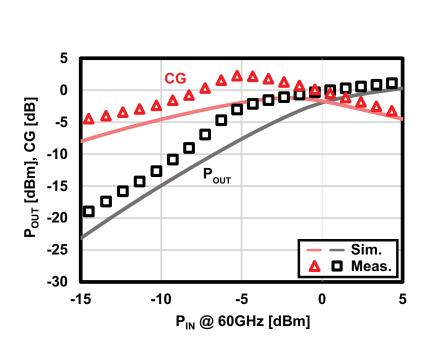

probe is used to connect the circuit output pad to the power sensor. The simulated and measured output power values of the proposed tripler are shown in Fig. 3.12. Around -2.9dBm output power is achieved with a bandwidth of around 27GHz. The measured fundamental signal rejection ratio (HRR1) is shown in Fig. 3.13(a). More than 10dB rejection is achieved around the center frequency similar to the second harmonic rejection ratio (HRR2) shown in Fig. 3.13(b).

The measured power in/out characteristics at 38GHz input frequency (114GHz output frequency) are shown in Fig. 3.14. The maximum conversion gain is around -13.5dB. The simulation results show good agreement with the measured results as can be seen in the graphs. Table 3.1 compares the performance of both proposed tripler and doubler circuits with the state-of-the-art CMOS frequency multipliers that operate at frequencies around

Figure 3.11: Measurement setup.

Figure 3.12: Tripler measured and simulated output power. (input power = 10dBm)

100GHz. The tripler achieves competitive performance with a very simple single-ended device non-linearity-based architecture thanks to the harmonic cancellation techniques, reducing the required area and DC power. Injection-locking-based designs as in [64] may show superior performance, but they require tuning due to the PVT variation as they are oscillator-based, not to mention the inclusion of buffers.

Table 3.1: Tripler Performance Comparison

|                             | This Work   | [64]      | [65]              |  |  |  |

|-----------------------------|-------------|-----------|-------------------|--|--|--|

| Process                     | 65nm CMOS   | 40nm CMOS | 130nm CMOS        |  |  |  |

| Frequency [GHz]             | 103-130     | 115-129   | 92-104            |  |  |  |

| Mult. Factor                | ×3          | ×3        | ×3                |  |  |  |

| Topology                    | Device NL\$ | ILFT#     | NLTL <sup>%</sup> |  |  |  |

| Max. CG [dB]                | -13.5       | N/A       | -12.2             |  |  |  |

| Max. P <sub>OUT</sub> [dBm] | -2.9        | 3         | -1.5              |  |  |  |

| HRR1* [dB]                  | 3.7-12.3    | > 38      | N/A               |  |  |  |

| HRR2** [dB]                 | 8.6-15.4    | > 20      | N/A               |  |  |  |

| P <sub>DC</sub> [mW]        | < 28        | 53.2      | 135               |  |  |  |

| Area [mm²]                  | 0.29        | 0.36      | 1.12              |  |  |  |

<sup>\*</sup> Fundamental rejection ratio. \*\* Second harmonic rejection ratio. \*Device non-linearity \* Injection-locking frequency tripler.

<sup>%</sup> Non-linear transmission line.

Figure 3.13: Tripler measured and simulated fundamental rejection ratio. (input power = 10dBm)

Figure 3.14: Tripler measured and simulated output power and Conversion gain.

Figure 3.15: Fundamental rejection stub (a) schematic (b) simulated stub impedance, (c) smith chart.

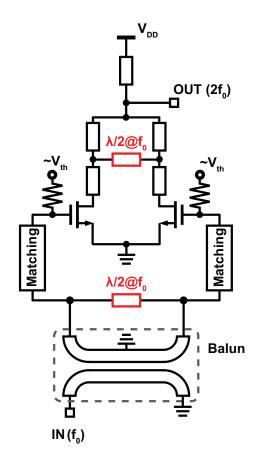

#### 3.2.2 Proposed Differential Tripler

As mentioned earlier in this section, the differential architecture automatically cancels the second harmonic at the tripler output due to the odd symmetry. However, the perfect symmetry is not possible in practical situations as balun and device mismatches cause the second harmonic common mode signal power to increase. The fundamental signal which is usually suppressed using stubs may still have high power at the output due to the non-ideal characteristics of the stubs. In this subsection, fundamental and second harmonic suppression techniques that utilize the differential properties are introduced.

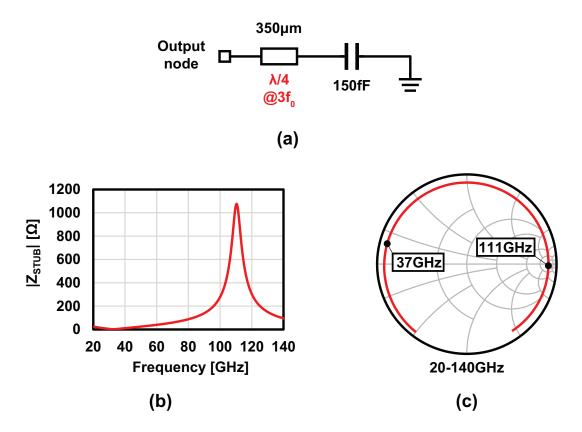

First, a fundamental frequency rejection stub illustrated in Fig. 3.15(a) is introduced. a quarter-wave stub at the third harmonic frequency is loaded with a purely capacitive reactance. The input impedance of the stub is calculated as in the following equation:

$$Z_{\rm in}(l) = Z_0 \frac{j(Z_0 \tan(\frac{2\pi}{\lambda}l) - \frac{1}{\omega C})}{Z_0 + j\frac{1}{\omega C} \tan(\frac{2\pi}{\lambda}l)}$$

(3.3)

where  $Z_{in}(l)$  is the input impedance of the stub with the transmission line length l,  $Z_0$  is the

Figure 3.16: Tripler circuit (input signal frequency =  $f_0$  = 38–39GHz): (a) Conventional differential tripler. (b) Proposed tripler circuit.

characteristic impedance of the transmission line (50  $\Omega$ ),  $\lambda$  is the electrical wavelength,  $\omega$  is the angular frequency, and C is the load capacitance. The capacitance value is optimized so that the stub looks as a short circuit at the fundamental frequency, while having a large impedance at the third harmonic to avoid any losses. Since the load is purely capacitive (ideally), the stub will act as an open or short when the imaginary part is equal to zero. Hence,

$$C = \frac{1}{Z_0 \omega \tan(\frac{2\pi}{\lambda} l)} \tag{3.4}$$

The optimal calculated C value using (3.4) is around 150fF.